Ports And Signals Part IV

Sunday, 24 October 2021 20:28

Semicon Editor 01

Resolved Vector Signals Resolved vector signals have same property as Resolved Logic Vectors. Resolved vector signals are used for connecting two resolved logic vector ports. One key issue is, Resolved Vector signals should not be driven outside a process/methods.

Last Updated ( Tuesday, 29 March 2022 00:49 )

Read more...

|

Ports And Signals Part III

Sunday, 24 October 2021 14:53

Semicon Editor 01

Resolved Logic Vectors

In real hardware, there are times when we need to model tristate bus. So that multiple agents can drive same bus. Like PCI bus or Microprocessor 8085 address and data bus.

Last Updated ( Tuesday, 29 March 2022 00:49 )

Read more...

Ports And Signals Part II

Thursday, 21 October 2021 21:55

Semicon Editor 01

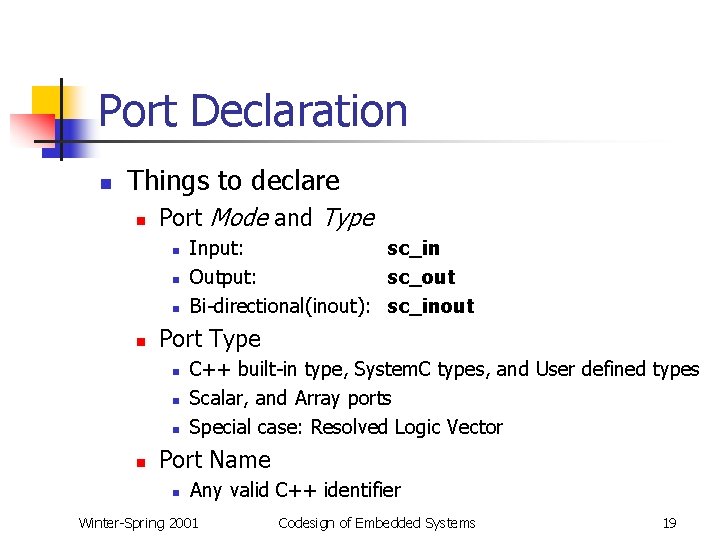

Array Of Ports/Signals SystemC allows to declare Array of ports and signals. This is very useful when we need to create array of similar ports and signals.

Last Updated ( Tuesday, 29 March 2022 00:49 )

Read more...

Ports And Signals Part I

Thursday, 21 October 2021 21:51

Semicon Editor 01

Introduction

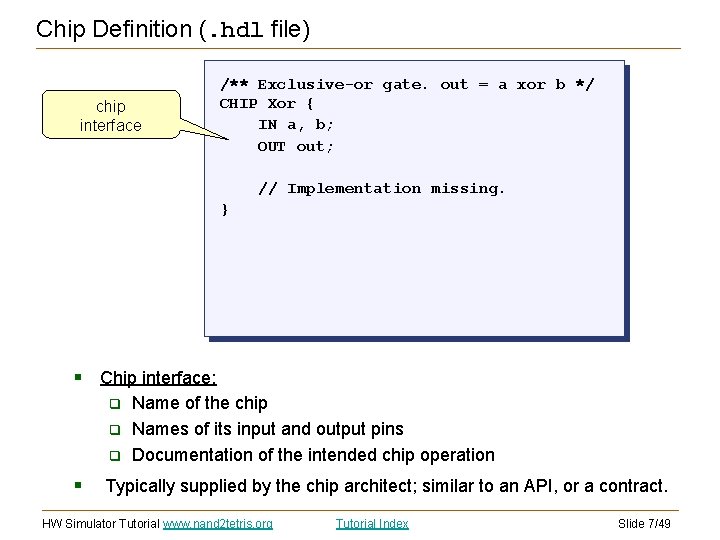

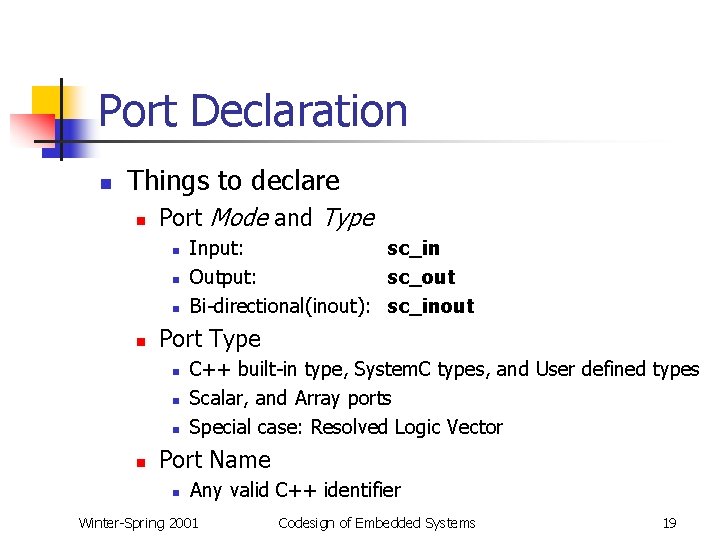

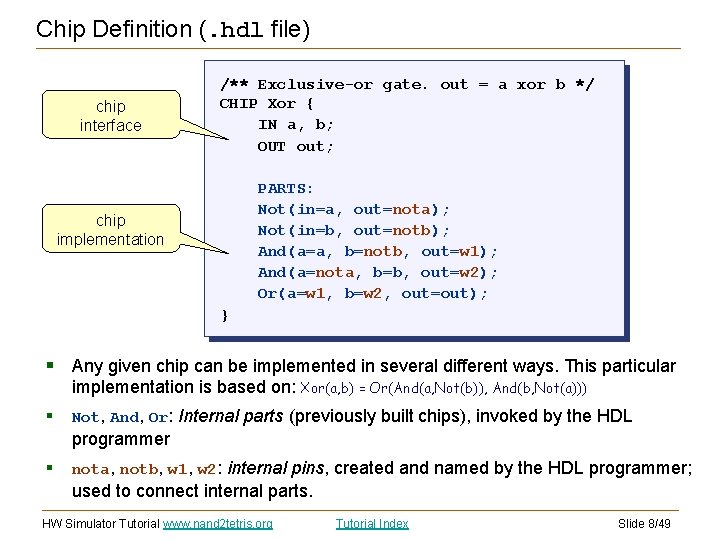

In this chapter we shall see ports and signal types in details. Accessing Ports/Signals

Last Updated ( Tuesday, 29 March 2022 00:49 )

Read more...

Channels In SystemC Part IV

Thursday, 21 October 2021 21:35

Semicon Editor 01

sc_fifo sc_fifo is a predefined primitive channel intended to model the behavior of a fifo, that is, a first-in first-out buffer. A fifo is an object of class sc_fifo. Each fifo has a number of slots for storing values.

Last Updated ( Tuesday, 29 March 2022 00:51 )

Read more...

Channels In SystemC Part III

Tuesday, 19 October 2021 19:43

Semicon Editor 01

sc_semaphore

sc_semaphore is a predefined primitive channel intended to model the behavior of a software semaphore as used to provide limited concurrent access to a shared resource. A semaphore has an integer value, the semaphore value, which is set to the permitted number of concurrent accesses when the semaphore is constructed.

Last Updated ( Tuesday, 29 March 2022 00:50 )

Read more...

Channels In SystemC Part II

Tuesday, 19 October 2021 19:40

Semicon Editor 01

sc_mutex sc_mutex is a predefined primitive channel intended to model the behavior of a mutual exclusion lock as used to control access to a resource shared by concurrent processes.

Last Updated ( Tuesday, 29 March 2022 00:50 )

Read more...

Channels In SystemC Part I

Tuesday, 19 October 2021 19:36

Semicon Editor 01

Â

Introduction Introduction

SystemC provides Channels for communication between two modules. This Channels make complex communication easy. SystemC has two types of channels. Â

Last Updated ( Tuesday, 29 March 2022 00:50 )

Read more...

Interfacing With HDL Simulator Part IX

Saturday, 16 October 2021 22:22

Semicon Editor 01

SystemVerilog DPI Interface SystemVerilog DPI is much more easy to interface with external C like languages. We can still use the exisiting TF and ACC routines. Below is same example shown with VPI.

Last Updated ( Tuesday, 29 March 2022 00:52 )

Read more...

Interfacing With HDL Simulator Part VIII

Saturday, 16 October 2021 22:20

Semicon Editor 01

VPI Interface File | Shown for VCS. Let me know if you want for modelsim or NcSim. | | Â | 1 #include

Last Updated ( Tuesday, 29 March 2022 00:52 )

Read more...

Interfacing With HDL Simulator Part VII

Saturday, 16 October 2021 22:16

Semicon Editor 01

SystemC Counter Exports 1 #ifndef COUNTER_TB_EXPORTS_H 2 #define COUNTER_TB_EXPORTS_H

Last Updated ( Tuesday, 29 March 2022 00:52 )

Read more...

Interfacing With HDL Simulator Part VI

Thursday, 14 October 2021 19:54

Semicon Editor 01

Verilog DUT 1 `timescale 1ns / 1ns 2 // Verilog DUT

Last Updated ( Tuesday, 29 March 2022 00:51 )

Read more...

Interfacing With HDL Simulator Part V

Thursday, 14 October 2021 19:49

Semicon Editor 01

Compile Commands # Point to your systemC home SYSTEMC_HOME = /appl/systemc

Last Updated ( Tuesday, 29 March 2022 00:51 )

Read more...

Interfacing With HDL Simulator Part IV

Thursday, 14 October 2021 19:47

Semicon Editor 01

SystemC Ports 1 #ifndef MEMORY_TB_PORTS_H 2 #define MEMORY_TB_PORTS_H

Last Updated ( Tuesday, 29 March 2022 00:51 )

Read more...

Interfacing With HDL Simulator Part III

Tuesday, 12 October 2021 19:25

Semicon Editor 01

SystemC TxGen Header File 1 #ifndef MEMORY_TXGEN_H 2 #define MEMORY_TXGEN_H

Last Updated ( Tuesday, 29 March 2022 00:51 )

Read more...

Interfacing With HDL Simulator Part II

Tuesday, 12 October 2021 19:22

Semicon Editor 01

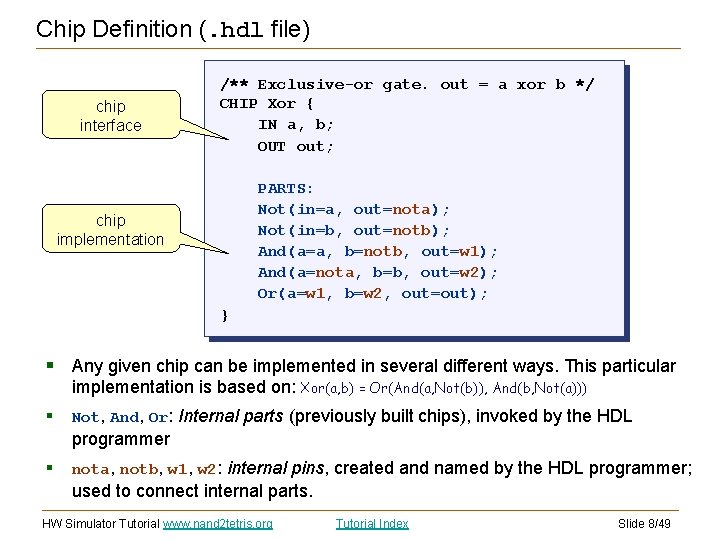

Verilog DUT 1 // Simple Verilog Memory Model 2 module memory(

Last Updated ( Tuesday, 29 March 2022 00:51 )

Read more...

|

|

|

|

|

|

|

Page 10 of 118 |