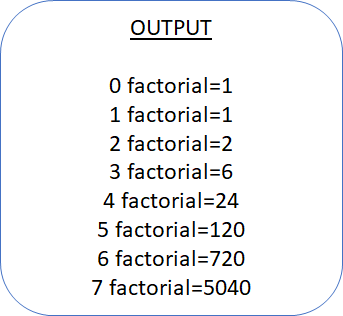

STATIC AND AUTOMATIC LIFETIME

Saturday, 18 September 2021 13:37

Semicon Editor 01

Static: For a variable static lifetime is, its memory never de-allocated until simulation ends. Automatic: For a variable Automatic lifetime is, it is stack storage of variable (for multiple entries to a task, function, or block,

Last Updated ( Saturday, 18 September 2021 13:39 )

Read more...

WEIGHTED DISTRIBUTION IN SYSTEM VERILOG

Saturday, 18 September 2021 13:28

Semicon Editor 01

In constraint random verification, it may take a long time for a particular corner case to be generated which scenario we never thought. Sometimes even after running test-case regression for N number of time corner case may not be generated and you may see holes in functional coverage.

Last Updated ( Saturday, 18 September 2021 13:31 )

Read more...

GENERATE RANDC BEHAVIOR FROM RAND VARIABLE

Thursday, 16 September 2021 18:44

Semicon Editor 01

It’s easy to get the first cycle of random numbers by pushing values on a list in post_randomize() and adding a constraint that keeps the values in the list excluded from the next solution.

Last Updated ( Thursday, 16 September 2021 18:46 )

Read more...

TYPES OF COVERAGE METRICS

Thursday, 16 September 2021 18:38

Semicon Editor 01

Coverage is used as a metric for evaluating the progress of a verification project. Coverage metric forms an important part of measuring progress in constrained random testbenches and also provides good feedback to the quality and effectiveness of constrained random testbenches.

Last Updated ( Tuesday, 29 March 2022 00:57 )

Read more...

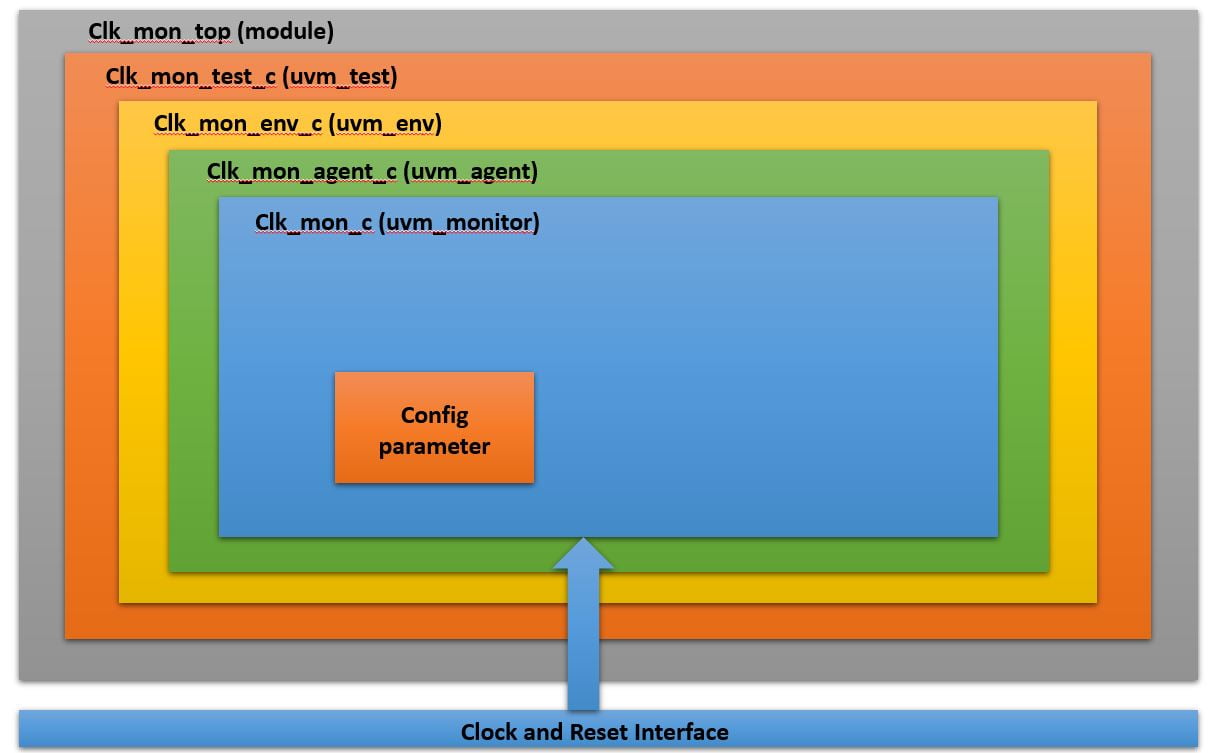

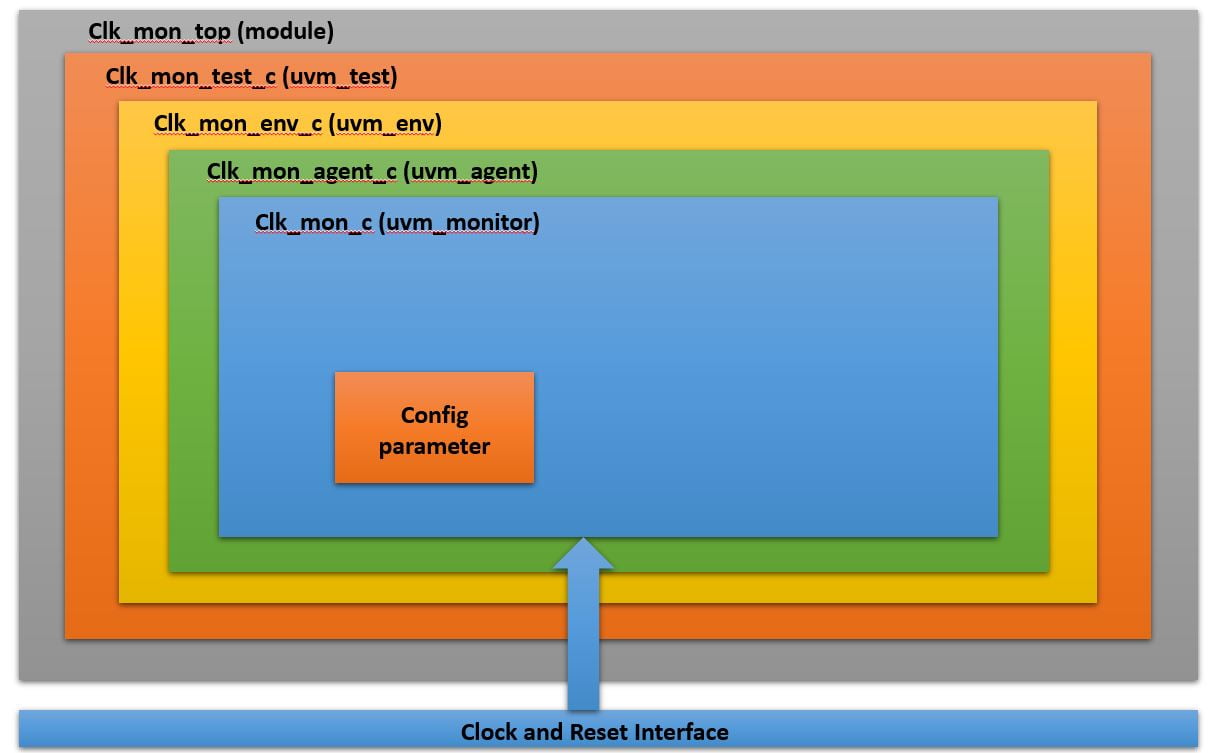

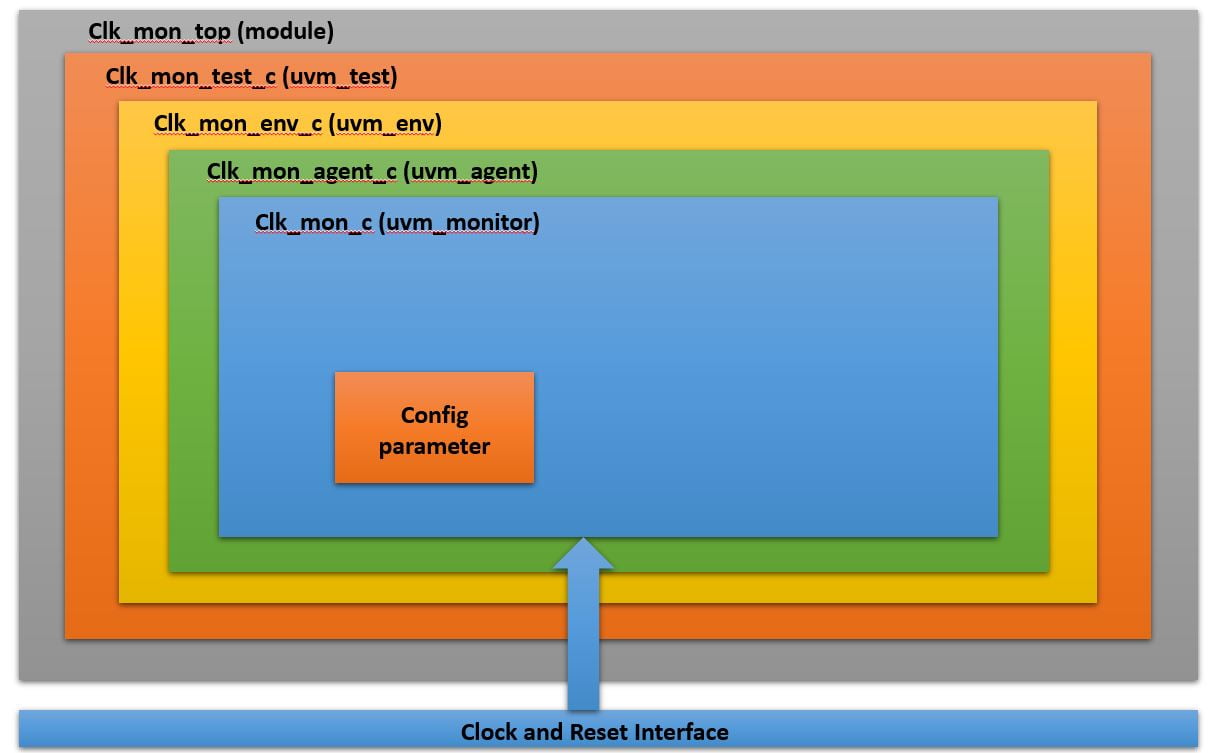

CLOCK MONITORS IN SOC VERIFICATION

Thursday, 16 September 2021 18:34

Semicon Editor 01

Introduction: As technologies advance, we see increasingly complex SoCs in the market, SoCs that have various wireless modules, and processors that use new bus architectures to communicate with them.

Last Updated ( Thursday, 16 September 2021 18:37 )

Read more...

STATIC AND AUTOMATIC LIFETIME

Tuesday, 14 September 2021 19:01

Semicon Editor 01

Static: For a variable static lifetime is , its memory never de-allocated until simulation ends. Automatic: For a variable Automatic lifetime is , it is stack storage of variable (for multiple entry to a task, function or block, it will have stack storage)

Last Updated ( Tuesday, 14 September 2021 19:06 )

Read more...

RANDOMIZE() VS STD::RANDOMIZE()

Tuesday, 14 September 2021 18:57

Semicon Editor 01

The built-in class randomize method operates exclusively on class member variables. Using classes to model the data to be randomized is a powerful mechanism that enables the creation of generic, reusable objects containing random variables and constraints that can be later extended

Last Updated ( Tuesday, 14 September 2021 19:00 )

Read more...

HOW TO GENERATE AN ARRAY OF UNIQUE RANDOM VALUES

Tuesday, 14 September 2021 18:46

Semicon Editor 01

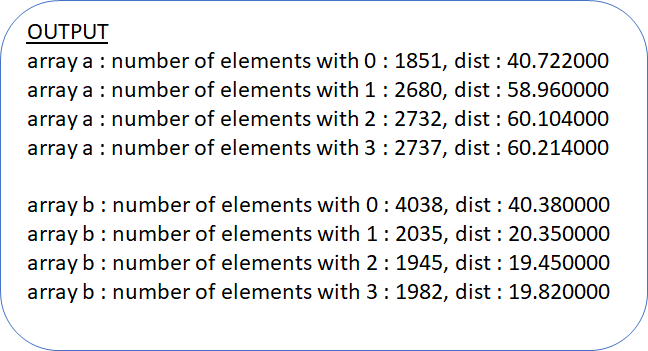

Now a days in many verification scenarios it require to create a set of random instructions or addresses with each unique values or we can say that no repeating values, usually represented as elements in a dynamic array.

Last Updated ( Tuesday, 14 September 2021 18:52 )

Read more...

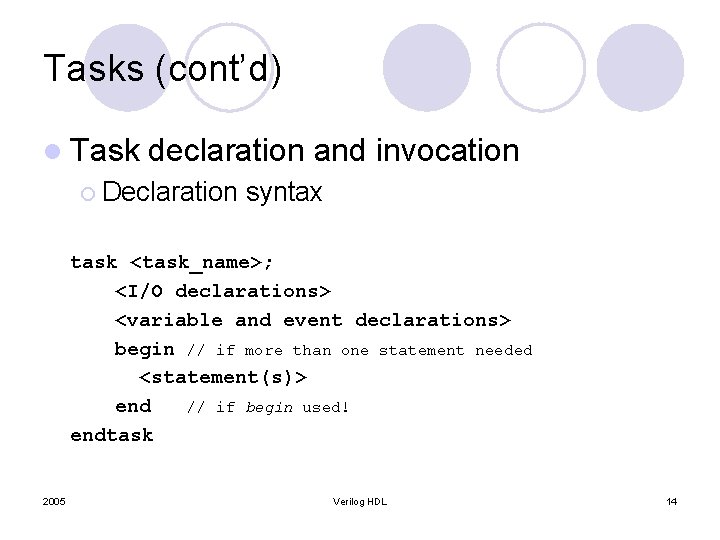

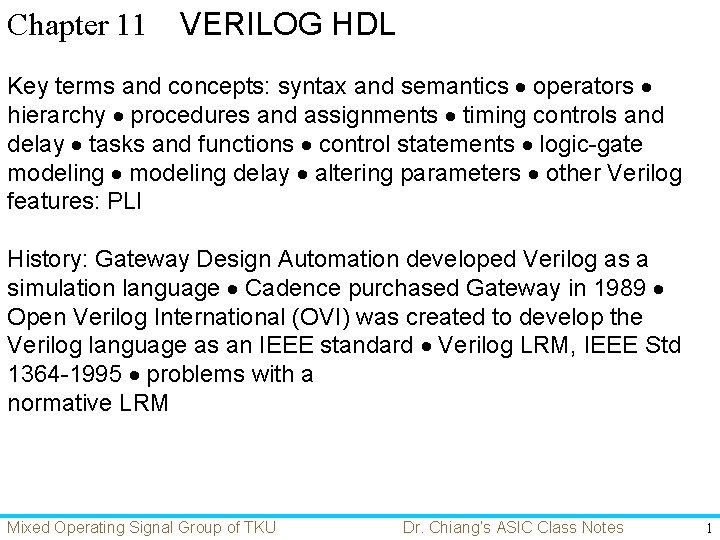

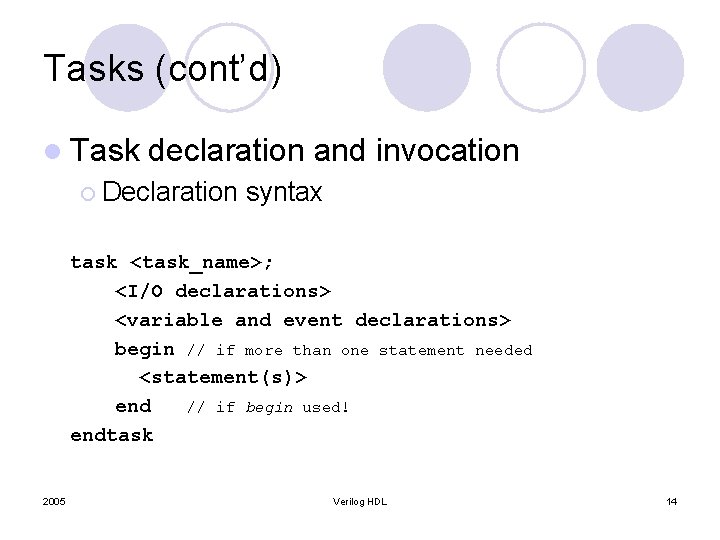

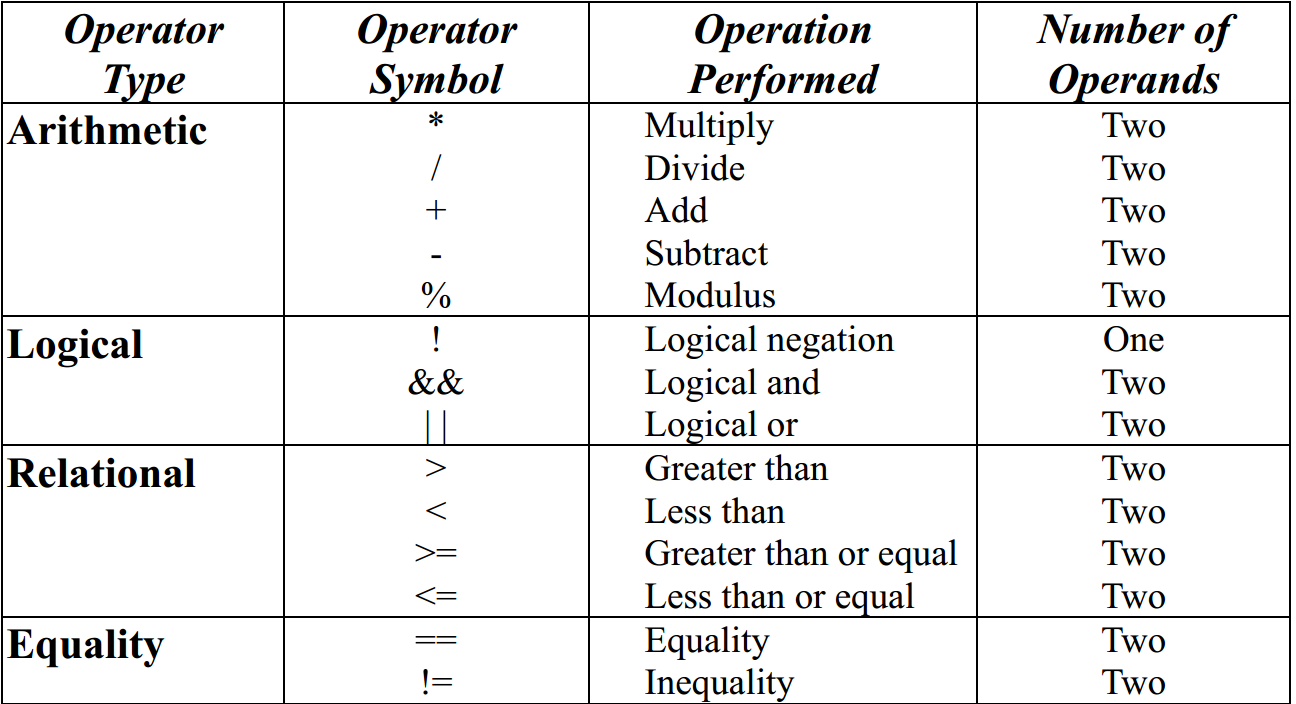

Verilog HDL Syntax And Semantics Part-VI

Sunday, 12 September 2021 17:52

Semicon Editor 01

Example - wor 1 module test_wor(); 2

Last Updated ( Tuesday, 29 March 2022 00:57 )

Read more...

Verilog HDL Syntax And Semantics Part V

Sunday, 12 September 2021 17:41

Semicon Editor 01

Hierarchical Identifiers Hierarchical path names are based on the top module identifier followed by module instant identifiers, separated by periods.

Last Updated ( Tuesday, 29 March 2022 00:57 )

Read more...

Verilog HDL Syntax And Semantics Part-IV

Sunday, 12 September 2021 17:32

Semicon Editor 01

Port Connection Rules Inputs : internally must always be of type net, externally the inputs can be connected to a variable of type reg or net.

Last Updated ( Tuesday, 29 March 2022 00:58 )

Read more...

Verilog HDL Syntax And Semantics Part-III

Saturday, 11 September 2021 13:57

Semicon Editor 01

Modules Modules are the building blocks of Verilog designs You create the design hierarchy by instantiating modules in other modules.

Last Updated ( Tuesday, 29 March 2022 00:58 )

Read more...

CLOCK MONITORS IN SOC VERIFICATION

Saturday, 11 September 2021 13:55

Semicon Editor 01

Introduction As technologies advance, we see increasingly complex SoCs in the market, SoCs that have various wireless modules, and processors that use new bus architectures to communicate with them.

Last Updated ( Saturday, 11 September 2021 13:57 )

Read more...

Verilog HDL Syntax And Semantics Part-II

Saturday, 11 September 2021 13:53

Semicon Editor 01

Numbers in Verilog You can specify constant numbers in decimal, hexadecimal, octal, or binary format. Negative numbers are represented in 2's complement form.

Last Updated ( Tuesday, 29 March 2022 00:58 )

Read more...

Verilog HDL Syntax And Semantics Part-I

Thursday, 09 September 2021 17:27

Semicon Editor 01

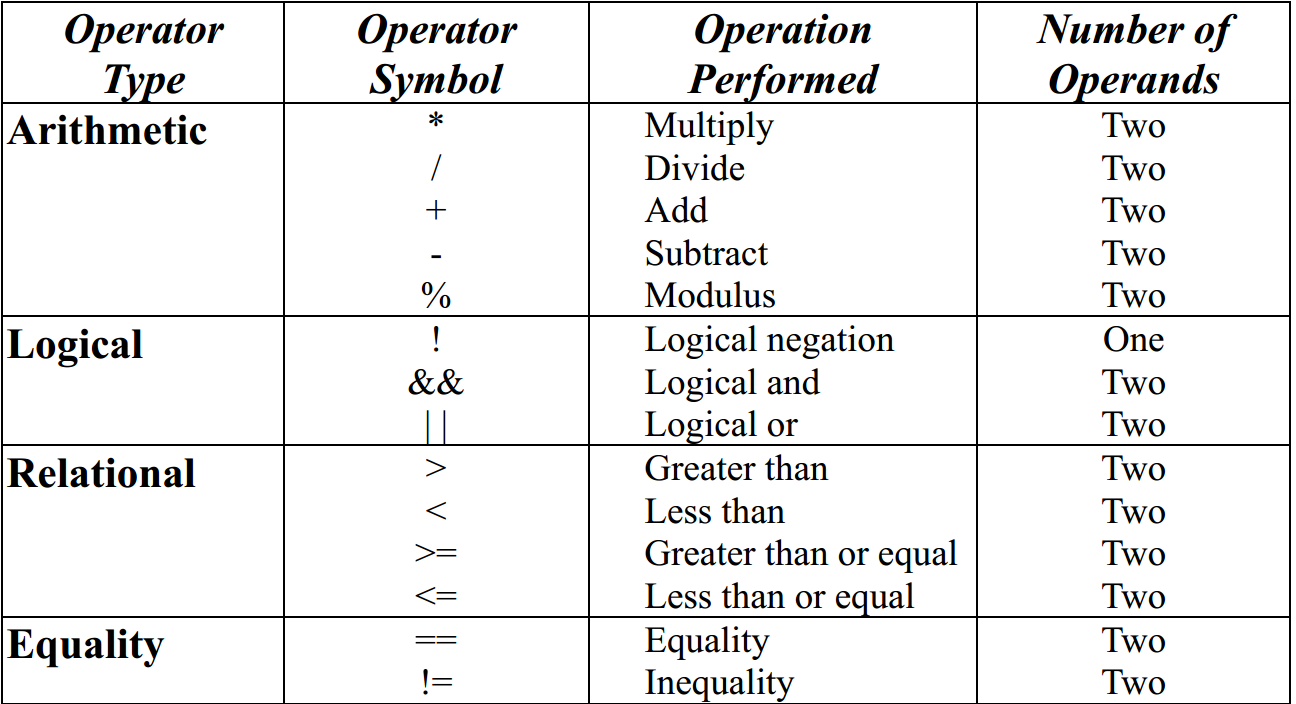

Lexical Conventions The basic lexical conventions used by Verilog HDL are similar to those in the C programming language. Verilog HDL is a case-sensitive language. All keywords are in lowercase.

Last Updated ( Tuesday, 29 March 2022 00:58 )

Read more...

|

|