Convergence , divergence and re-convergence

Tuesday, 28 September 2021 14:43

Semicon Editor 01

Now a days , multiple clocks in a system are common due to increasing frequency and complexity. A CDC check is a must check on the design before tapping out as any CDC violation may be fatal and could be a cause of chip failure.

Last Updated ( Tuesday, 28 September 2021 14:45 )

Read more...

WEIGHTED DISTRIBUTION IN SYSTEM VERILOG

Tuesday, 28 September 2021 14:38

Semicon Editor 01

In constraint random verification, it may take a long time for a particular corner case to be generated which scenario we never thought. Sometimes even after running test-case regression for N number of time corner case may not be generated and you may see holes in functional coverage.

Last Updated ( Tuesday, 29 March 2022 00:55 )

Read more...

CONSTRAINT OVERRIDE IN SYSTEM VERILOG

Sunday, 26 September 2021 20:11

Semicon Editor 01

Here in this overriding of constraint if we will have the same constraint name in the parent class as well as child class then we can say that our constraint is overridden in the child class.

Last Updated ( Tuesday, 29 March 2022 00:55 )

Read more...

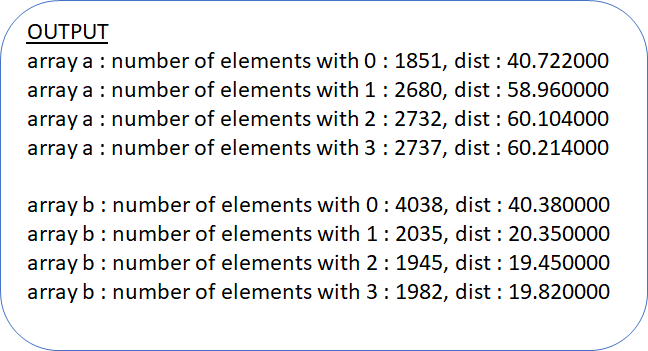

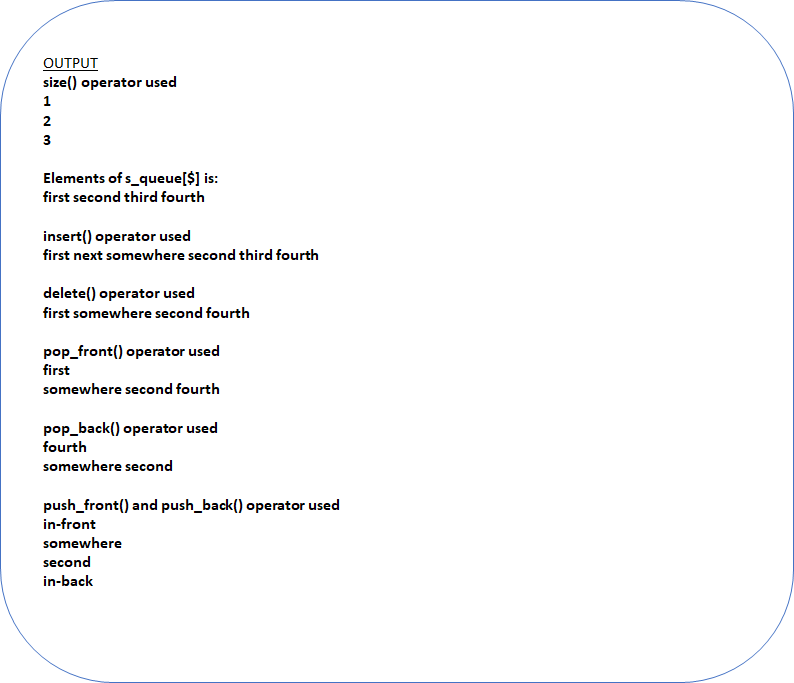

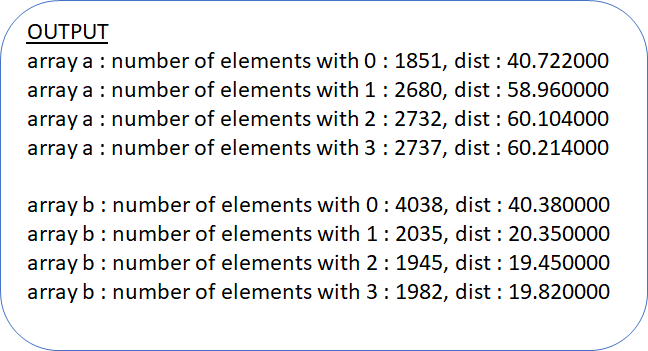

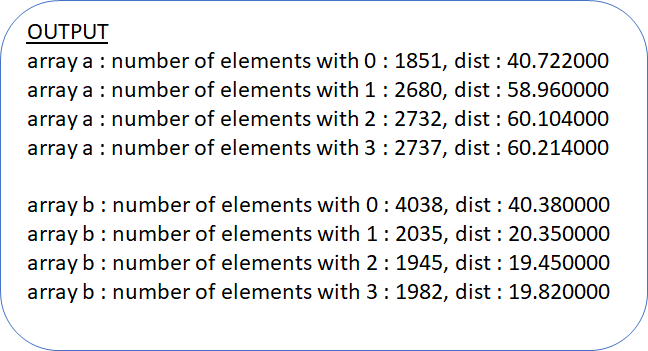

DIFFERENT ARRAY TYPES AND QUEUES IN SYSTEM VERILOG

Sunday, 26 September 2021 20:05

Semicon Editor 01

Dynamic Array: Usage of dynamic array when user to allocate its size for storage during run time.Dynamic array store a contiguous collection of data.

Last Updated ( Tuesday, 29 March 2022 00:55 )

Read more...

Verilog code for 8b/10b encoder and decoder

Sunday, 26 September 2021 20:00

Semicon Editor 01

8b/10b is used mainly for clock recovery in serial communication. With this coding, the serial line will always get a balanced stream of 0's and 1's which give enough switching of 0's and 1's level on the line. It is called DC balancing. Using this encoding will result in 25% overhead in the data stream , meaning to transmit 80-bits , you will actually transmit 100-bits.

Last Updated ( Tuesday, 29 March 2022 00:53 )

Read more...

Serial Peripheral Interface - SPI

Saturday, 25 September 2021 14:04

Semicon Editor 01

Serial Peripheral Interface - SPI (adsbygoogle = window.adsbygoogle || []).push({ google_ad_client: "ca-pub-9050238130712788", enable_page_level_ads: true }); Serial Peripheral Interface Bus

Last Updated ( Saturday, 25 September 2021 14:07 )

Read more...

A Sample file for Synthesis

Saturday, 25 September 2021 13:55

Semicon Editor 01

Design Specification Design Specification A counter having 2 input clocks, clk_a running at 100 MHz and clk_B running at 200MHz. there are clock divider for clk_A in design.

Last Updated ( Saturday, 25 September 2021 14:03 )

Read more...

Verilog code for parity checker

Saturday, 25 September 2021 13:52

Semicon Editor 01

In the case of even parity, the number of bits whose value is 1 in a given set are counted. If that total is odd, the parity bit value is set to 1, making the total count of 1's in the set an even number. If the count of ones in a given set of bits is already even, the parity bit's value remains 0.

In the case of odd parity, the situation is reversed. Instead, if the sum of bits with a value of 1 is odd, the parity bit's value is set to zero.

Last Updated ( Saturday, 25 September 2021 13:54 )

Read more...

SEMAPHORE IN SYSTEMVERILOG

Thursday, 23 September 2021 14:30

Semicon Editor 01

A semaphore allows you to control access to a resource. Conceptually, a semaphore is a bucket. When a semaphore is allocated, a bucket that contains a fixed number of keys is created.

Last Updated ( Tuesday, 29 March 2022 00:56 )

Read more...

WEIGHTED DISTRIBUTION IN SYSTEM VERILOG

Thursday, 23 September 2021 13:50

Semicon Editor 01

In constraint random verification, it may take a long time for a particular corner case to be generated which scenario we never thought. Sometimes even after running test-case regression for N number of time corner case may not be generated and you may see holes in functional coverage.

Last Updated ( Tuesday, 29 March 2022 00:56 )

Read more...

PCI Express - Overview

Thursday, 23 September 2021 13:47

Semicon Editor 01

PCI Express ( Peripheral Component Interconnect Express ), PCI Express ( Peripheral Component Interconnect Express ), is a high speed serial computer expansion bus standard. It is designed to replace the older version of PCI like PCI/PCI-X standard. Difference in Normal Pci and Pci-Express ->

Last Updated ( Thursday, 23 September 2021 13:50 )

Read more...

DIGITAL VERIFICATION

Functional Verification is often the most resource intensive and costly part of the SoC hardware design process. Semicon’s engineering team can starting verification early in the design cycle by streamlining testbench development, facilitating faster turnaround times and high quality, reliable designs. Semicon’s expertise covers a comprehensive range of skills including test plan creation, testbench development and design debug at both IP block and SoC level. We are able to bring the latest testbench verification methodologies such as UVM VIP development, ABV and metric driven verification. - Feature extraction from Specification.

- Develop test plan which includes stimulus generation plan, functionality checking and coverage modeling.

- Review the test plan with Design team.

- Develop testbench environment and other components for verifying each block in design.

- Create necessary test cases to ensure desired functionality of each block.

- Run Regression tests at block level and report bugs in RTL.

- Create directed and randomized test cases to check corner cases in design.

- Integrate all blocks and reuse block level verification components to verify the design at system level.

- Run tests at system level to ensure correct block integration. Proceed with system level regression testing to verify system functionality and generate coverage reports.

ADVANTAGES OF UVM OVER SV

Sunday, 19 September 2021 16:09

Semicon Editor 01

UVM is a standard verification methodology which is getting standardized as IEEE 1800.12 standard. UVM consists of a defined methodology in terms of architecting testbenches and test cases, and also comes with a library of classes that helps in building efficient constrained random testbenches easily.

Last Updated ( Sunday, 19 September 2021 16:10 )

Read more...

HOW TO TERMINATE UVM TEST? (UVM OBJECTIONS)

Sunday, 19 September 2021 16:05

Semicon Editor 01

As we know that in Traditional Directed Testbenches, we used to terminate a Test by calling a Verilog System Task i.e. $finish after the required steps like reset, configuration, data transfer and self-checking are completed.

Last Updated ( Sunday, 19 September 2021 16:08 )

Read more...

WEIGHTED DISTRIBUTION IN SYSTEM VERILOG

Sunday, 19 September 2021 16:01

Semicon Editor 01

In constraint random verification, it may take a long time for a particular corner case to be generated which scenario we never thought. Sometimes even after running test-case regression for N number of time corner case may not be generated and you may see holes in functional coverage.

Last Updated ( Tuesday, 29 March 2022 00:56 )

Read more...

|

|

Low power design is not a new area, but it was not that much important as it is now.

Low power design is not a new area, but it was not that much important as it is now.

Low power design is not a new area, but it was not that much important as it is now.

Low power design is not a new area, but it was not that much important as it is now.