UVM Analysis Components

Thứ ba, 03 Tháng 8 2021 14:46

Semicon Editor 01

Any type of Testbench typically requires following two sections to verify a targeted DUT:Stimulus Generation Analysis of the Design Response

Lần cập nhật cuối ( Thứ ba, 03 Tháng 8 2021 14:48 )

Đọc thêm...

Wait for Interface Signals in UVM

Chủ nhật, 01 Tháng 8 2021 19:18

Semicon Editor 01

In normal scenarios the synchronization of hardware events, like clocks, resets, error signals, interrupts etc., primarily takes place inside the UVM Driver & Monitors for an UVM Testbench.

Lần cập nhật cuối ( Chủ nhật, 01 Tháng 8 2021 19:24 )

Đọc thêm...

SystemVerilog Data Hiding

Chủ nhật, 01 Tháng 8 2021 19:06

Semicon Editor 01

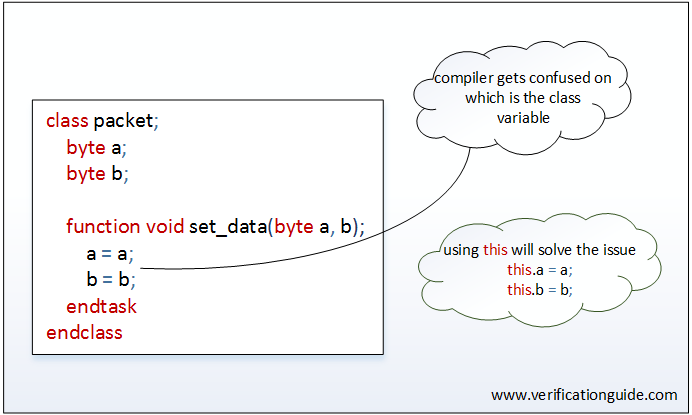

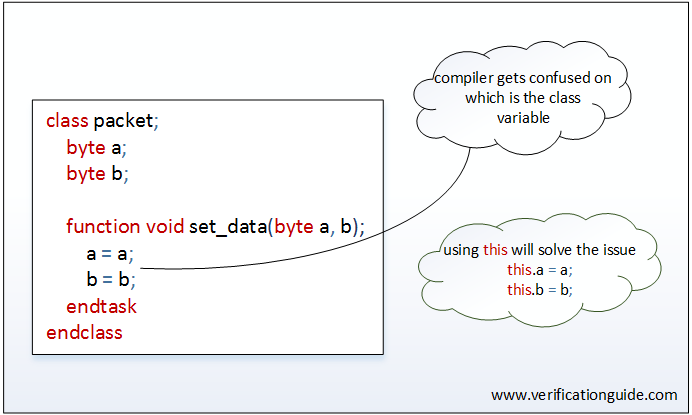

Many times we might use the Base Classes or Base Class library provided by other teams or third party sources. We’ve seen how to access the Class Properties and Methods i.e. “Class Members” in SystemVerilog using the Class Handles. By default, These Class Members are Public in nature. It means these Class

Lần cập nhật cuối ( Chủ nhật, 01 Tháng 8 2021 19:14 )

Đọc thêm...

SystemVerilog OOP – Part 2

Thứ bảy, 31 Tháng 7 2021 19:13

Semicon Editor 01

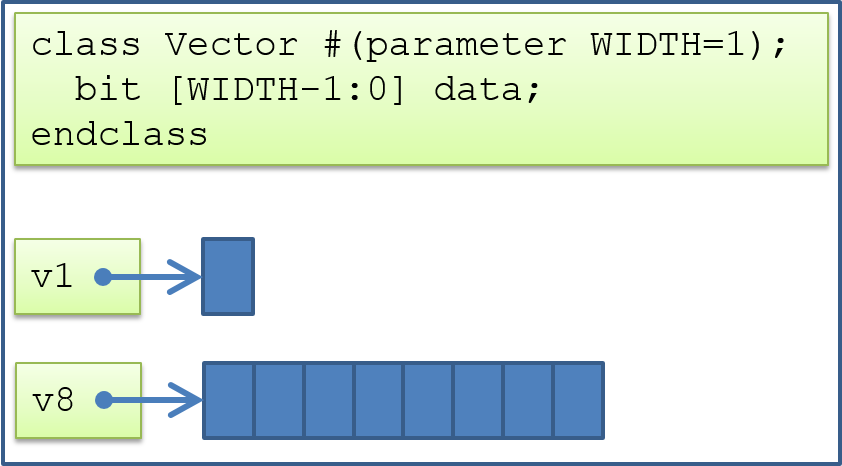

Hii! Welcome to SystemVerilog OOP – Part 2. I hope you’ve already gone through SystemVerilog OOP – Part 1, where we touched base with different key concepts in OOP like Encapsulation, Inheritance, Data Hiding, Parametrizaton & Polymorphism.

Lần cập nhật cuối ( Thứ bảy, 31 Tháng 7 2021 19:15 )

Đọc thêm...

SystemVerilog OOP – Part 1

Thứ bảy, 31 Tháng 7 2021 19:03

Semicon Editor 01

Hello All!, I wanted to write for SystemVerilog category since a long time but UVM Testbench Architecture category contains so many interesting topics to write about that whenever I wanted I fall-in for the Testbench category.

Lần cập nhật cuối ( Thứ bảy, 31 Tháng 7 2021 19:09 )

Đọc thêm...

UVM Sequence Arbitration

Thứ năm, 29 Tháng 7 2021 15:14

Semicon Editor 01

Before explaining the Sequence Arbitration lets have a very quick Sequences recap – UVM Sequences are used to generate input stimulus for the Design Under Test i.e. DUT. Sequences are executed on a particular Sequencer which passes the generated Transactions to the connected Driver.

Lần cập nhật cuối ( Thứ năm, 29 Tháng 7 2021 15:17 )

Đọc thêm...

Interrupt Handling in UVM?

Thứ năm, 29 Tháng 7 2021 15:06

Semicon Editor 01

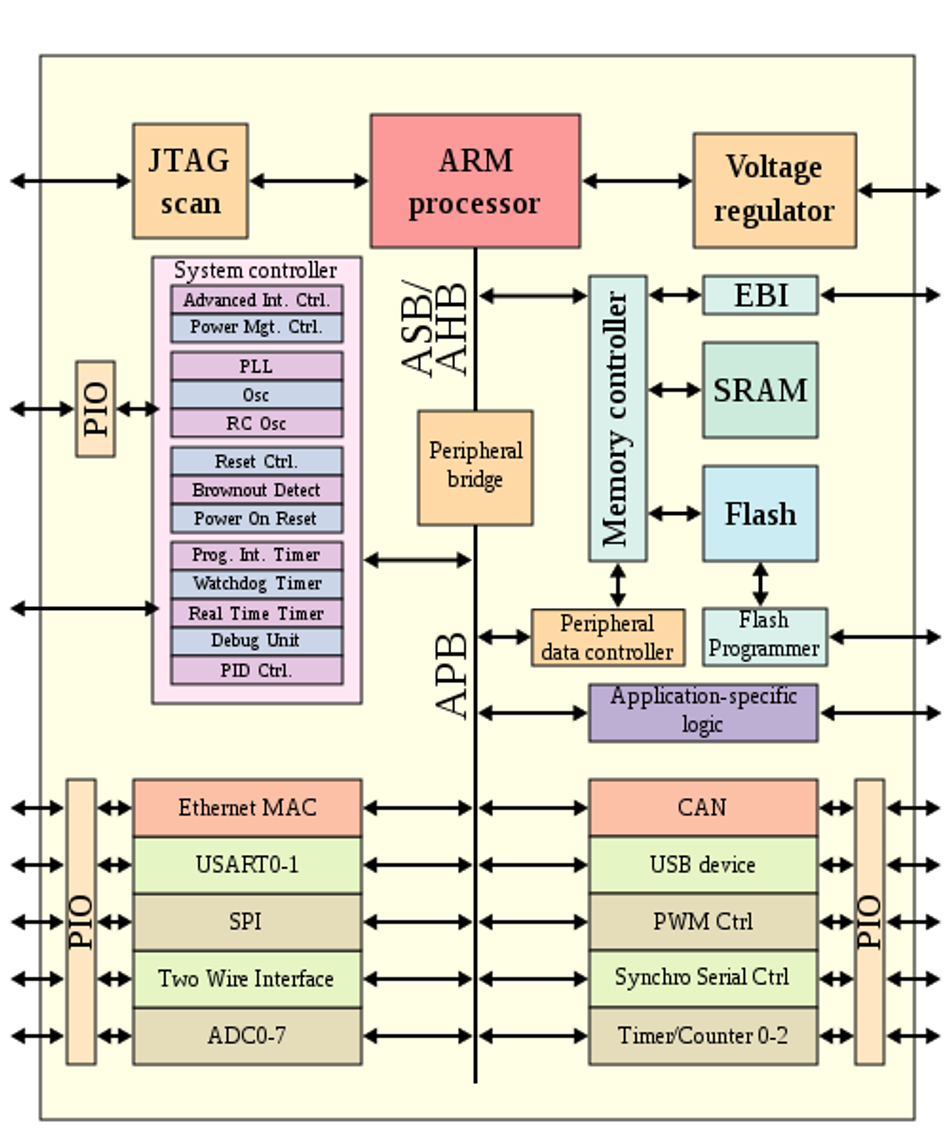

Interrupt handling is a well known feature of any SoC which usually comprises of CPU, Bus Fabric, several Controllers, Sub-Systems & many IP blocks as part of it. In some way or other Interrupts are used to act as the sideband signals of the Design/IP Blocks & most of time its not the part of main bus or control bus.

Lần cập nhật cuối ( Thứ năm, 29 Tháng 7 2021 15:11 )

Đọc thêm...

Application of Virtual Interface and uvm_config_db

Thứ ba, 27 Tháng 7 2021 16:11

Semicon Editor 01

How to connect the DUT to the UVM Testbench..??In our traditional directed Testbench environments, all the components are “static” in nature & information (data/control) is also exchanged in the form

Lần cập nhật cuối ( Thứ ba, 27 Tháng 7 2021 16:20 )

Đọc thêm...

The way “UVM Hierarchical Sequences” works?

Thứ ba, 27 Tháng 7 2021 16:03

Semicon Editor 01

We discussed about “Sequences” in my previous post titled “UVM Sequences and Transactions Application“. Here, we’ll talk about “Hierarchical Sequences“. Following are the questions most likely pops-up into our mind the moment we think about Hierarchical Sequences.

Lần cập nhật cuối ( Thứ ba, 27 Tháng 7 2021 16:11 )

Đọc thêm...

What is Coverage Metrics?

Chủ nhật, 25 Tháng 7 2021 15:19

Semicon Editor 01

Hi Friends, in my previous Functional Coverage blog, I’ve shared high level idea & understanding about Coverage & types of Coverage i.e. Code Coverage & Functional Coverage with an example of Coverage data model i.e. cover groups.

Lần cập nhật cuối ( Chủ nhật, 25 Tháng 7 2021 15:21 )

Đọc thêm...

UVM Driver Use Models – Part 2

Chủ nhật, 25 Tháng 7 2021 15:01

Semicon Editor 01

Hi! As we already know that UVM Driver plays a very significant role in interface protocol implementation since it deals with class based transaction or sequence items on one side and on the other side works at clock based signal/pin level activities.

Lần cập nhật cuối ( Chủ nhật, 25 Tháng 7 2021 15:14 )

Đọc thêm...

UVM Driver Use Models – Part 1

Chủ nhật, 25 Tháng 7 2021 14:48

Semicon Editor 01

Since it is evident that Driver is a component in the UVM environment which deals with transaction or sequence item and transform it into pin level signal activities in temporal domain by following a particular protocol or use model & vice versa.

Lần cập nhật cuối ( Chủ nhật, 25 Tháng 7 2021 15:01 )

Đọc thêm...

Deprecated Features in UVM 1.2

Thứ năm, 22 Tháng 7 2021 13:03

Semicon Editor 01

There are many features which are deprecated in latest UVM 1.2 standard. If you’re switching to use UVM 1.2 in your projects, its a MUST not to use following methods, variables, macros & parameters in your code & update

Lần cập nhật cuối ( Thứ năm, 22 Tháng 7 2021 13:06 )

Đọc thêm...

Introduction about Advanced Functional Verification

Thứ năm, 22 Tháng 7 2021 12:53

Semicon Editor 01

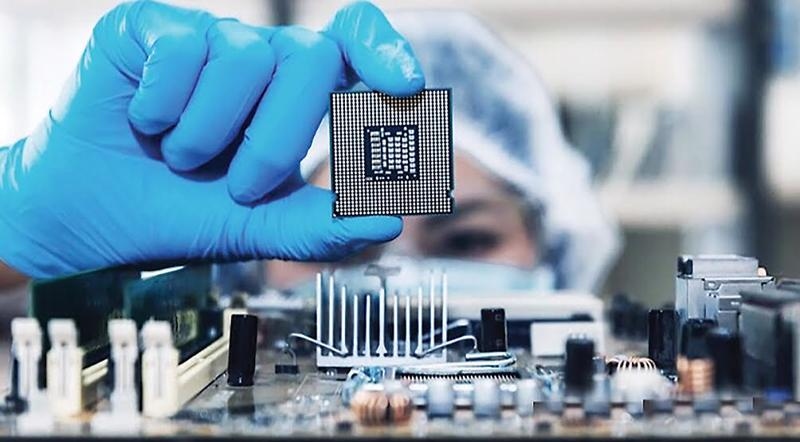

Electronic gadgets are an integral part of our day-to-day life. Lifeline of these gadgets/products are semiconductor IC/SoC/ASIC/FPGA which are mounted on the PCB (Printed Circuit Boards) & connected with each other to make the gadget operational.

Lần cập nhật cuối ( Thứ năm, 22 Tháng 7 2021 12:58 )

Đọc thêm...

TLM FIFO Implementation

Thứ năm, 22 Tháng 7 2021 12:45

Semicon Editor 01

As we have seen that TLM put() & TLM get() methods are blocking in nature. What does that mean? In fact, during put() and get() method execution, there is a single process running which passes the control from the port to the export & back again.

Lần cập nhật cuối ( Thứ năm, 22 Tháng 7 2021 12:48 )

Đọc thêm...

|

|