Verilog Quick Reference part 1

Saturday, 28 August 2021 14:00

Semicon Editor 01

This is still in very early stage, need time to add more on this. MODULE module MODID[({PORTID,})];

Last Updated ( Tuesday, 29 March 2022 01:00 )

Read more...

|

Verilog Synthesis Tutorial Part-III

Thursday, 26 August 2021 20:19

Semicon Editor 01

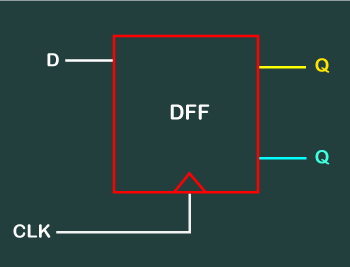

Logic Circuit Modeling From what we have learnt in digital design, we know that there could be only two types of digital circuits. One is combinational circuits and the second is sequential circuits. There are very few rules that need to be followed to get good synthesis output and avoid surprises.

Last Updated ( Tuesday, 29 March 2022 01:01 )

Read more...

Verilog Synthesis Tutorial Part-II

Thursday, 26 August 2021 20:12

Semicon Editor 01

Constructs Not Supported in Synthesis

Last Updated ( Tuesday, 29 March 2022 01:01 )

Read more...

Verilog Synthesis Tutorial Part-I

Thursday, 26 August 2021 19:26

Semicon Editor 01

What is logic synthesis ? Logic synthesis is the process of converting a high-level description of design into an optimized gate-level representation. Logic synthesis uses a standard cell library which have simple cells, such as basic logic gates like and,

Last Updated ( Tuesday, 29 March 2022 01:01 )

Read more...

Assertions In Verilog Part - III

Sunday, 22 August 2021 21:11

Semicon Editor 01

Assertion with OVL Now that we have seen the code of FIFO and the testbench, let's see the example of using OVL to build assertions for the FIFO. To use OVL, we need to first install the OVL package.

Last Updated ( Tuesday, 29 March 2022 01:02 )

Read more...

Assertions In Verilog Part - II

Sunday, 22 August 2021 21:02

Semicon Editor 01

Verification Of FIFO Our first example is the verification of a synchronous FIFO. Here we will build a simple testbench around the FIFO model and use simple assertions to show how they can be used to check simple protocols. If you have any better suggestion, please let me know.

Last Updated ( Tuesday, 29 March 2022 01:02 )

Read more...

Assertions In Verilog Part-I

Sunday, 22 August 2021 20:52

Semicon Editor 01

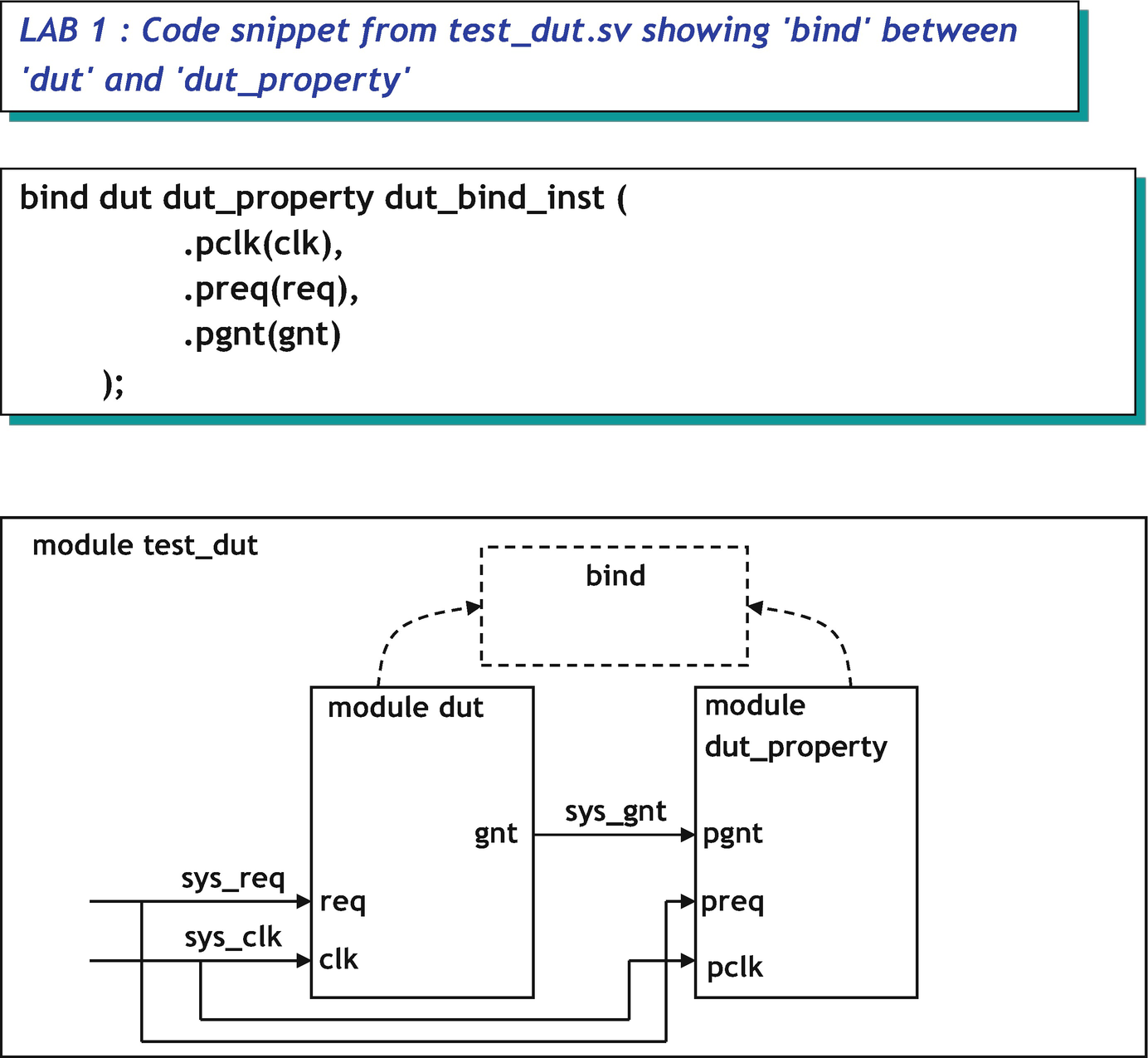

Intrucdition: Verification with assertions refers to the use of an assertion language to specify expected behavior in a design, and of tools that evaluate the assertions relative to the design under verification.

Last Updated ( Tuesday, 29 March 2022 01:02 )

Read more...

Verilog PLI Tutorial Part IV

Sunday, 22 August 2021 20:27

Semicon Editor 01

Verilog Procedural Interface (VPI) The Verilog Procedural Interface (VPI) is a C-programming interface for the Verilog Hardware Description Language (HDL). VPI is the third-generation procedural interface to Verilog HDL.

Last Updated ( Tuesday, 29 March 2022 01:03 )

Read more...

Verilog PLI Tutorial Part-III

Saturday, 21 August 2021 14:56

Semicon Editor 01

PLI Routines.PLI 1.0 provides two types of routines, they are access routines task and function routines.

Last Updated ( Tuesday, 29 March 2022 01:03 )

Read more...

Verilog PLI Tutorial Part-2

Saturday, 21 August 2021 14:19

Semicon Editor 01

Writing PLI application: The example that we saw was too basic and is no good for any practical purpose. Let's consider our infamous counter example and write the DUT reference model and Checker in C and link that to the Verilog Testbench.

Last Updated ( Tuesday, 29 March 2022 01:02 )

Read more...

Verilog PLI Tutorial - part 1

Saturday, 21 August 2021 14:02

Semicon Editor 01

Introduction Verilog PLI (Programming Language Interface) is a mechanism to invoke C or C++ functions from Verilog code. The function invoked in Verilog code is called a system call. An example of a built-in system call is $display, $stop, $random. PLI allows the user to create custom system calls, something that Verilog syntax does not allow us to do. Some of these are:-

Last Updated ( Tuesday, 29 March 2022 01:02 )

Read more...

PASSING STRUCTS AND UNIONS

Thursday, 19 August 2021 14:51

Semicon Editor 01

Passing Structure Example DPI allows to pass the structs and Unions . This can be done by passing pointers or by packing. In the following example, a "struct" is passed from SystemVerilog to C and also from C to Systemverilog using import and export functions.

Last Updated ( Thursday, 19 August 2021 14:53 )

Read more...

Open Arrays SystemVerilog

Thursday, 19 August 2021 14:48

Semicon Editor 01

Open Arrays The size of the packed dimension, the unpacked dimension, or both dimensions can remain unspecified,such cases are referred to as open arrays (or unsized arrays). Open arrays allow the use of generic code to handle different sizes.

Last Updated ( Thursday, 19 August 2021 14:50 )

Read more...

DATA TYPES

Thursday, 19 August 2021 14:39

Semicon Editor 01

The SystemVerilog DPI supports only SystemVerilog data types, which are the data types that can cross the boundary between SystemVerilog and a foreign language in both the direction. On the other hand, the data types used in C code shall be C types. A value that is passed through the DPI is specified in SystemVerilog code as a value of SystemVerilog data type,

Last Updated ( Thursday, 19 August 2021 14:44 )

Read more...

Import Methods

Tuesday, 17 August 2021 14:23

Semicon Editor 01

Import Methods Methods implemented in C and given import declarations in SystemVerilog can be called from SystemVerilog, such methods are referred to as imported methods.Imported tasks or functions are similar to SystemVerilog tasks or functions.

Last Updated ( Tuesday, 17 August 2021 14:27 )

Read more...

Two Layers Of Dpi-C

Tuesday, 17 August 2021 14:20

Semicon Editor 01

Two Layers Of Dpi-C DPI-C consists of two separate layers: the SystemVerilog layer and a foreign language layer. The SystemVerilog layer does not depend on which programming language is actually used as the foreign language.

Last Updated ( Tuesday, 17 August 2021 14:22 )

Read more...

|

|

|

|

|

|

|

Page 15 of 118 |