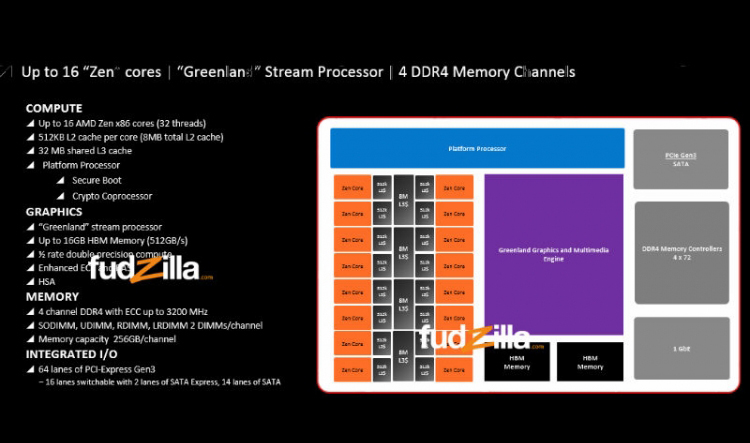

Theo trang Fudzilla, kiến trúc APU sắp tới của AMD mang tên Zen sẽ sử dụng thiết kế dạng monolithic (tạm dịch là nguyên khối).

Mỗi nhân CPU Zen sẽ có bộ nhớ L2 512KB của riêng mình, trái ngược với cache L2 được chia sẻ chung đang được hãng áp dụng từ thời kiến trúc Bulldozer tới nay (thiết kế dạng module). Điều này sẽ giúp cải thiến tốc độ và hiệu quả truy cập dữ liệu của vi xử lý.

Chỉ có cấp độ cache cuối cùng là L3 8MB mới được chia sẻ giữa mỗi bốn nhân mà thôi. Một con chip Zen có thể sở hữu tối đa 16 nhân, như vậy là có 16 bộ nhớ cache L2 và 4 bộ nhớ cache L3.

Nó còn được tích hợp công nghệ SMT (Simultaneous multithreading, tương tự như siêu phân luồng của Intel), lúc đó hệ điều hành sẽ nhận biết được số nhân ảo (còn gọi là nhân logic) gấp đôi số nhân thực (tức nếu có 16 nhân thực thì sẽ có 32 nhân logic).

Hiện chưa rõ bao giờ thì các APU Zen sẽ được ra mắt, nhưng nhiều khả năng nó sẽ không dành cho thị trường tiêu dùng mà sẽ nhắm đến các máy chủ hiệu năng cao.

Nguồn: tinhte.vn