Với sự phát triển của công nghệ mới, các thiết kế được tích hợp trong một hệ thống lớn hơn gọi là System-on-Chip (SOC). Tuy nhiên ngày nay do sự giới hạn của công suất tiêu tán trong các ứng dụng di động mà các thiết kế có xu hướng chia nhỏ ra thành nhiều khối có tác vụ giống nhau để có thể chia sẻ hoạt động một cách hợp lý tùy thuộc vào quy mô của ứng dụng. Hệ thống đó gọi là Multi-core hay Multi-system, trong thiết kế vi xử lý đó là kỹ thuật Multi-Processor System-on-Chip (MPSoCs).

Những thiết kế SOCs đầu tiên sử dụng kỹ thuật chia sẻ bus chung vì tính đơn giản của nó. Tuy nhiên với những thiết kế MPSoCs quy mô lớn thì vấn đề về băng thông và hiệu suất lại xảy ra. Trước tiên, ta phân tích một số cấu trúc bus phổ biến.

Chia sẻ trên một bus

Cấu trúc bus truyền thống là các master và ngoại vi (point) giao tiếp với nhau trên cùng một hệ thống bus. Các point buộc phải được phân xử và chờ cấp quyền sử dụng bus, kỹ thuật này thường được gọi đơn giản là point-to-point. Kỹ thuật này làm tăng các dây nối và các điểm liên kết. Các kết nối dư thừa sẽ làm tăng công suất của mạch và độ trễ của hệ thống.

Thông thường, cấu trúc này chỉ đáp ứng tối đa 5 lõi cho một bộ phân xử.

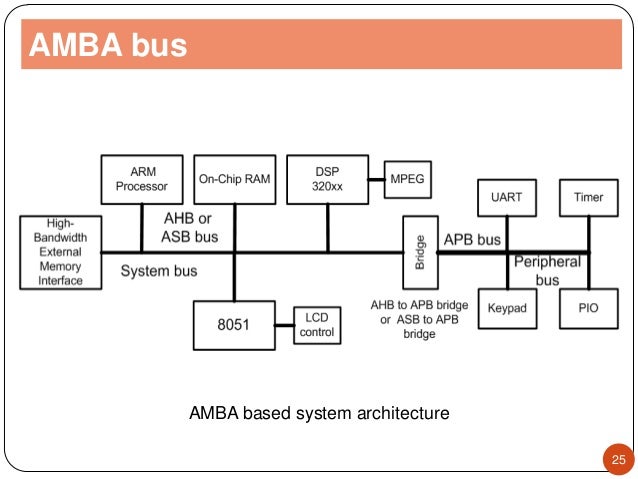

Cấu trúc Hierarchical/Segmented

Để giảm tải cho các nút quan trọng, cấu trúc bus phân cấp được dùng để phân vùng các khối thiết kế theo ứng dụng và tốc độ. Điều này giúp tối ưu hóa công suất tiêu thụ, vì các ngoại vi tần số thấp không cần thiết phải chạy với tần số quá cao. Ví dụ tiêu biểu cho cấu trúc này là hệ thống AMBA và IBM CoreConnect được sử dụng rất rộng rãi. Các phân khúc bus hệ thống được giảm tải do số ngoại vi kết nối giảm. Tuy nhiên, dữ liệu và thông điệp truyền tải trong trường hợp bus phân cấp cần phải chuẩn hóa khác nhau trên từng đoạn, gây phức tạp trong thiết kế và gỡ rối.

Bus Crossba

Bus Crossbar được hình thành bằng cách kết hợp các cơ cấu dọc và ngang tạo thành mạng lưới chuyển mạch. Điều này khắc phục được vần đề kết nối song song của các hệ thống bus trước. Các điểm truy xuất có thể diễn ra đồng thời theo kiểu point-to-point.

Mặc dù hệ thống bus này giúp cải thiện băng thông và tận dụng được những băng thông rảnh rỗi, nhưng nó cũng làm tăng các liên kết và module đếm theo cấp số nhân. Hậu quả là tài nguyên và năng lượng tăng cao.

Bus Crossbar còn được gọi là bus lập phương. Một hạn chế nữa của bus Crossbar là trễ RC lớn, làm giảm tốc độ xung clock tối đa của hệ thống. Và cuối cùng, bus Crossbar rất khó có thể mở rộng số lượng module gắn vào hệ thống như hệ thống bus chia sẻ hay bus phân cấp.

Hệ thống bus cơ bản và hệ thống Crossbar được ứng dụng rộng rãi kể từ khi chúng mới xuất hiện. Nhưng với những thiết kế phức tạp, cần phải có một mô hình kết nối mới giải quyết các hạn chế của các hệ thống cũ. Một ý tưởng đó là hệ thống bus chia sẻ và phân đoạn theo thông tin của thiết bị. Hệ thống này cung cấp sự tiện lợi và có khả năng mở rộng cao. Cấu trúc của hệ thống này được mô tả giống như một mạng định tuyến, gọi là NoC.

Network-on-Chip

NoCs xuất hiện lần đầu vào năm 2000 do Hermani công bố.

Cấu trúc Noc chia sẻ tài nguyên giữa những kết nối định tuyến bằng các đoạn liên kết ngắn nhất. Hệ thống sẽ chọn các đường kết nối tối ưu nhất giữa hai điểm (point). Rõ ràng, kết nối giữa hai điểm cố định là một đường truyền thường xuyên thay đổi, đường truyền này là tối ưu nhất tại thời điểm xác lập kết nối. Các module được định danh (ví dụ như địa chỉ IP) và giao tiếp qua một giao diện gọi là NI (Network Interface).

Các dữ liệu truyền dẫn được đóng gói và truyền đi theo địa chỉ đã định trước. Như vậy, bất cứ module nào kết nối vào hệ thống này đều có cơ chế giám sát thông tin trên bus.

Những thiết kế MPSoCs có thể định nghĩa kích thước dữ liệu giao tiếp cố định hay thay đổi theo các header. Do tính chất chuẩn hóa và tái sử dụng mà hệ thống NoCs giảm thiểu thời gian thiết kế chip. Nghiên cứu của Arteris cho thấy với cấu trúc NoCs có thể giảm đến 40% các dây kết nối, giảm kích thước thiết kế cũng như giảm thời gian lay-out thiết kế.

Cấu trúc cell trong hệ thống NoCs

Một cell trong hệ thống NoCs được gọi là “microrouter”. Trong ví dụ trên, mỗi cell định tuyến có 5 FIFO ngõ vào có độ rộng cố định tương thích với các bộ xử lý và bộ định tuyến khác trong hệ thống. Ngõ ra không có FIFO đệm. Dữ liệu được lấy mẫu theo từng chu kỳ và ghi vào bộ đệm. Bộ định tuyền xác định dữ liệu ngõ ra (và trạng thái có hay không) dựa vào thông tin trong gói dữ liệu nhận được. Dữ liệu được chọn lại tiếp tục được đóng gói thông tin cho các tầng tiếp theo. Chu kỳ trên lặp lại cho các tầng sau theo đường đi đã được xác định (định tuyến tối ưu).

Hình sau cho thấy kết nối giữa các cell trong hệ thống:

Đường đi được định tuyến theo tọa độ. Thuật toán định tuyến được mô tả giống như hoạt động của một mạng internet thông thường.

Ứng dụng của hệ thống NoCs

Hiện nay, ưng dụng của hệ thống bus NoCs vẫn còn đang tiếp tục phát triển, đặc biệt là các ứng dụng Multi-SoCs, hệ thống vi xử lý đa lõi. Trên thực tế, hệ thống là sự mô phỏng của mạng thông tin giữa các nút và các điểm xử lý trung gian gọi là router.

Nguồn: icdesignvn

Mong Muốn Có Thêm Cơ Hội Trong Công Việc

Và Trở Thành Một Người Có Giá Trị Hơn

Bạn Chưa Biết Phương Thức Nào Nhanh Chóng Để Đạt Được Chúng

Hãy Để Chúng Tôi Hỗ Trợ Cho Bạn. SEMICON

Hotline: 0972.800.931 - 0938.838.404 (Mr Long)