Để thiết kế ra một sản phần phần cứng ( thường gọi là CHIP, và từ nay về sau trong bài viết sẽ gọi CHIP ) thường sẽ phải trải qua rất nhiều giai đoạn, công đoạn khác nhau.

Tùy theo mức độ phức tạp về chức năng, độ lớn của CHIP và độ khó của công nghệ, thời gian làm ra CHIP sẽ khác nhau. Tuy nhiên, sản xuất CHIP thường có quy trình như sau:

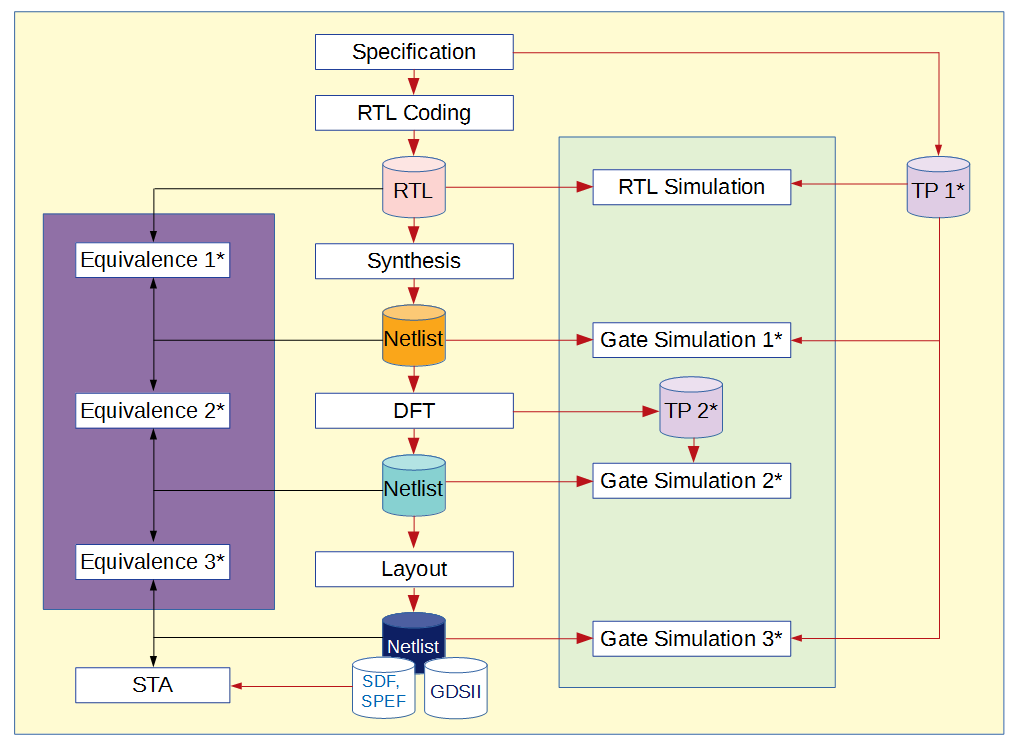

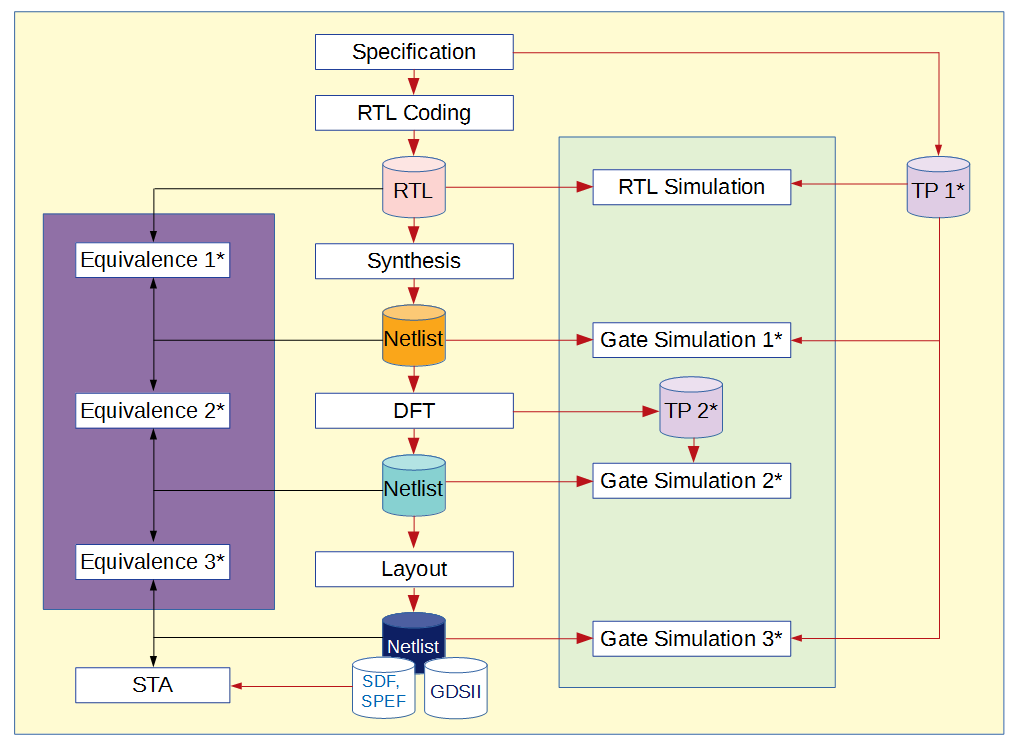

Đây là quy trình rất điển hình.

Tùy công ty hoặc tập đoàn mà quy trình này có thể có sự điều chỉnh.

1. Specification:

Đây là các phần mô tả và yêu cầu về chức năng logic cũng như các yêu cầu về physical, timing dành cho CHIP.

Các yêu cầu này được mô tả từ phía khách hàng. Ở một số khâu của thiết kế, các kỹ sư phải làm rõ nội dung của các đặc tả này thành các tài liệu chi tiết hơn. Mục đích của việc này là để xác nhận lại với phía khách hàng các yêu cầu một cách cụ thể trước khi bắt tay vào thiết kế.

Ngoài các đặc tả chi tiết của thiết kế, ở bước này kỹ sư cũng đã có thể thiết kế cả mô tả cho testbench và hệ thống mô phỏng, trong đó, các quy định về dữ liệu, waveform chuẩn ( đầu ra mong muốn của các test pattern) là vô cùng quan trọng.

Nếu như không xác nhận thường xuyên với khách hàng về yêu cầu của họ ngay từ đầu, rất dễ dẫn đến việc mất thời gian để sửa chữa lại và thiết kế lại từ đầu. Với thiết kế ASIC, việc thiết kế lại từ đầu làm tốn khá nhiều vốn và tài nguyên về con người.

2. RTL coding:

Sau khi có các yêu cầu về Logic, kỹ sư bắt đầu vào thực hiện việc coding.

Công đoạn này đòi hỏi kỹ sư phải vạch ra các khối chức năng một cách cụ thể, chi tiết và xác nhận với khách hàng ý tưởng và nhu cầu của họ. Đảm bảo việc có cùng chung suy nghĩ và hiểu biết về chức năng của thiết kế là một yếu tố quyết định đến sự thành công và hiệu quả của khâu RTL coding.

Không chỉ có làm việc RTL coding, kỹ sư còn phải làm kế hoạch cho việc mô phỏng ( simulation, logic verification ) cho RTL code mình thiết kế ra. Công việc này đòi hỏi khá nhiều kinh nghiệm và kỹ năng quản lý thiết kế.

Đầu ra của công đoạn này dĩ nhiên là các file code. Nó sẽ là đầu vào của 2 bước tiếp theo là Simulation và Synthesis.

3. RTL Simulation.

Ở bước này, thiết kế được kiểm chứng về mặt chức năng. Có nhiều phương pháp khác nhau để tiến hành. Các bạn có thể tìm hiểu thêm những từ khóa như OVM, UVM, hoặc traditional verification...

Đầu vào của bước này bao gồm kết quả của 2 bước trước đó: RTL code và Testbench ( bao gồm Test patterns ). TP *1 được tạo ra từ bước 1 và 2.

Đầu ra của simulation thông thường là waveform, data, hoặc các ràng buộc theo yêu cầu của bước trước. Quá trình simulation kết thúc khi tất cả các test pattern đều được thực thi và cho kết quả giống như kết quả mong đợi.

4. Synthesis:

Nói ngắn gọn, đây là bước chuyển design ở dạng code, sang dạng cổng logic. Dựa vào các quy ước về syntax của RTL code và các loại cell có trong library mà Tool sẽ map RTL code sang dang Gate. Bước này bắt đầu sử dụng đến các thư viện cell ( technology library ). Bước này cũng là lần đầu tiên, các bạn sẽ thấy được sự liên quan về logic với các yếu tố vật lý khác như độ trễ ( delay ), tốc độ, diện tích và năng lượng tiêu hao. Kết quả của bước Synthesis này là tiền đề cho các bước tiếp theo trong cả quy trình thiết kế. Trong đó, đối tượng output chính là Gate Level Netlist.

Để thực hiện được bước này, như đã nói, chúng ta cần RTL code, thư viện cell và một số yêu cầu về tần số, timing delay ... Các yêu cầu này được mô tả trong một file gọi là SDC ( Synopsys Design Constraints ).

4. Design For Test ( DFT )

Để phục vụ cho việc kiểm chứng các cổng logic trên CHIP san khi được sản xuất, người ta thường kiểm tra chúng tại nhà máy. Việc kiểm tra này thường đựa thực hiện bởi các máy Tester. Đầu vào của các máy test này là các mẫu thử, được tạo ra bởi các kỹ sư DFT.

Sau khi Synthesis xong, chúng ta có được Gate Level Netlist của design. Kỹ sư DFT sẽ tiến hành chèn thêm các mạch phục vụ cho việc test bên trên. Đồng thời, dựa vào đặc điểm và cấu trúc của design, kỹ sư DFT sẽ tạo ra các mẫu thử thông qua việc vận hành các Tool đặc thù cho DFT. Các mẫu thử này phải được kiểm tra trên Gate Level Design trước, sau đó, nếu kết quả OK thì mới được mang đi test trên CHIP thật tại nhà máy. Ở đây, mẫu thử hay test pattern được ký hiệu là TP *2

5. Layout

Layout là bước tiếp theo, sử dụng Netlist sau khi chèn DFT circuit. Tại bước này, có một quy trình riêng khá phức tạp cho công việc của các kỹ sư Layout. Họ sẽ phải sắp đặt các cell có trong Netlist sao cho thỏa mãn các yên cầu về sự sắp xếp này từ phía khách hàng. Ví dụ như, diện tích của CHIP, vị trí các IO, vị trí các memory, macro v.v. Tiếp theo họ sẽ phải giải quyết vấn đề quan trọng, đó là Timing, để đảm bảo các yêu cầu về tốc độ, các quy định, ràng buộc từ phía khách hàng và từ nhà máy sản xuất vv.

Ngoài ra, kỹ sư Layout còn phải làm việc về các vấn đề liên quan đến physical như áp, dòng, các lỗi DRC ( Design Rule Check ).

Sản phẩm cuối cùng của bước này là file GDSII. File này được giao cho phía nhà máy để người ta tiến hành các bước tiếp theo để sản xuất ra CHIP trên wafer.

6. STA ( Static Timing Analysis )

Đây là bước có liên quan mật thiết với bước số 5. STA sử dụng dữ liệu ( Netlist + SDF hoặc Netlist + SPEF ) từ Layout để tính toán Timing dựa vào timing constraint ( SDC ). Ở bước này, chúng ta cần đảm bảo tất cả các Constraint ( Ràng buộc ) đều thõa mãn (MET).

7. Equivalence:

Bước này có mục đích để kiểm tra tính tương đồng về logic giữa 2 designs nào đó. Ở bước này, kết quả có thể là Passed hoặc Failed. Nếu kết quả Failed, toàn bộ các bước sau đó của qui trình thiết kế bị xem như vô nghĩa. Do đó, kỹ sư có trách nhiệm tìm hiểu vấn đề và phát hiện ra nguyên nhân và đề xuất cách khắc phục.

Có thể so sánh giữa RTL với Netlist, Netlist với Netlist. Trong đó, Netlist có thể là Netlist ở những bước khác nhau trong quy trình thiết kế. Thông thường, Netlist được chia theo phase như:

- Pre-DFT Netlist: Netlist sau khi synthesis mà chưa được chèn mạch DFT

- Post-DFT Netlist: Netlist sau khi đã được chèn mạch DFT

- Post-CTS: Netlist post-DFT được làm qua bước CTS ( Clock Tree Synthesis )

- Post-Route: Netlist sau khi làm Routing

Cách gọi này có thể thay đổi tùy theo quy định của từng công ty, tập đoàn.

8. Gate simulation:

Phần này ý nghĩa tương tự như bước số 3. Tuy nhiên, đối tượng đầu vào của Simulation thay vì RTL code thì là Netlist.

Phần Gate Simulation được chia thành 2 loại:

- No Delay Simulation. Chạy simulation cho Gate Level mà không bao gồm thông tin delay của Cell và Net

- Back-Annotation Simulation. Chạy simulation cho Gate Level có bao gồm cả thông tin delay của Cell và Net. Thông tin Delay đó được lấy từ SDF file của bước Layout.

Phần test pattern của bước này không khác gì so với Test pattern của RTL simulation. Nhưng môi trường mô phỏng sẽ có sự khác nhau do những đặc tính khác nhau của RTL code và Gate Level Netlist.

Các từ viết tắt:

RTL: Register Transfer Level

TP: Test Pattern

DFT: Design For Test

SDF: Standard Delay Format

SPEF: Standard Parasitics Extraction Format

Nguồn: degic.freeforums

Mong Muốn Có Thêm Cơ Hội Trong Công Việc

Và Trở Thành Một Người Có Giá Trị Hơn

Bạn Chưa Biết Phương Thức Nào Nhanh Chóng Để Đạt Được Chúng

Hãy Để Chúng Tôi Hỗ Trợ Cho Bạn. SEMICON

Hotline: 0972.800.931 - 0938.838.404 (Mr Long)