Để code FlipFlop, chúng ta cũng sẽ cần đến sự phân biệt các loại tín hiệu có trong thiết kế phần cứng. Chủ yếu, chúng ta quan tâm đến 2 loại là reg và wire. Ngoài ra, chúng ta cần sử dụng phép gán Non-Blocking cho logic bên trong FlipFlop.

1. FlipFlop syntax:

*Đối với FlipFlop, luôn luôn sử dụng phép gán Non-Blocking ( <= )

Về cơ bản, cấu trúc verilog của một FlipFlop là như sau:

a, Loại không có reset, dưới đây sử dụng sườn lên của clock làm tín hiệu kích hoạt.

always @ ( posedge clock ) begindata <= new_data;

end

Nếu bạn muốn sử dụng sườn xuống thì vẫn có thể được. Cú pháp như sau:

always @ ( negedge clock ) begindata <= new_data;

end

b, Reset bất đồng bộ:

Dưới đây là code syntax cho FlipFlop tích cực cạnh lên của clock, reset tích cực ở mức thấp.

always @ ( posedge clock or negedge reset_n ) beginif ( ! reset_n ) begin

data <= 8'h00;

end

else begin

data <= new_data;

end

end

c, Reset đồng bộ:

FlipFlop với clock tích cực sườn lên, tín hiệu reset tích cực mức thấp.

always @ ( posedge clock ) beginif ( ! reset_n ) begin

data <= 8'h00;

end

else begin

data <= new_data;

end

end

d, Ví dụ về FlipFlop có logic phức tạp hơn:

Về cơ bản thì FlipFlop chỉ bao gồm mạch có phép gán Non-Blocking cho Q:

Q <= D;

Trong đó:

D là một mạch tổ hợp được viết ở các khối khác, có thể là dùng assign hoặc always block khác. ( Tham khảo thêm cách viết mạch tổ hợp ở bài khác )

Tuy nhiên, nếu Logic của D đơn giản, người ta có thể viết gộp cả logic của D và Q vào cú pháp của FlipFlop.

Do đó, các bạn có thể có các loại FlipFlop được viết như dưới đây:

FlipFlop với logic của D được viết bằng câu lệnh điều kiện if... else

always @ ( posedge clock ) beginif ( ! reset_n ) begin

data <= 8'h00;

end

else begin

if ( condition_1 ) begin

data <= new_data_1;

end

else begin

data <= new_data_2;

end

end

end

và một ví dụ nữa, logic của data được viết bằng case:

always @ ( posedge clock ) beginif ( ! reset_n ) begin

data <= 8'h00;

end

else begin

case ( option )

3'b000: data <= new_data + 8'h01;

3'b001: data <= new_data - 8'h55;

3'b010: data <= new_data + 8'h88;

3'b100: data <= new_data + 8'h33;

default: data <= new_data - 8'h44;

endcase

end

end

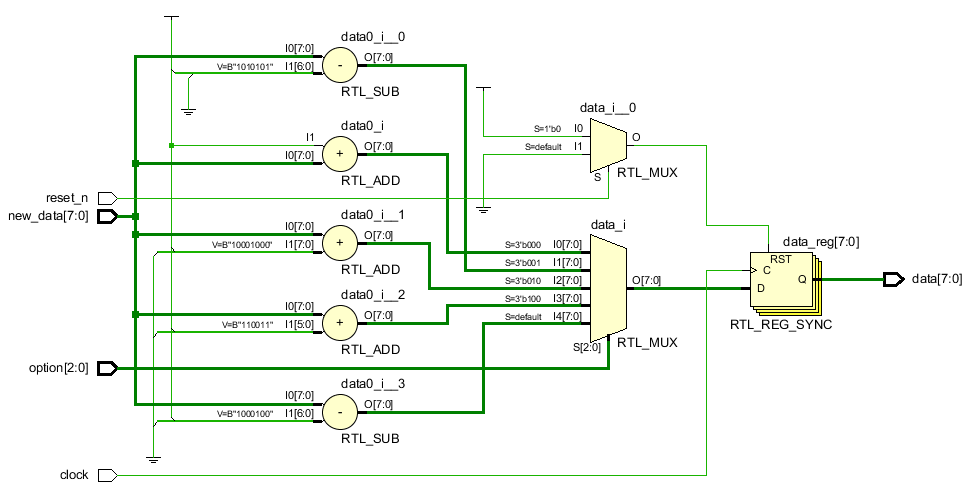

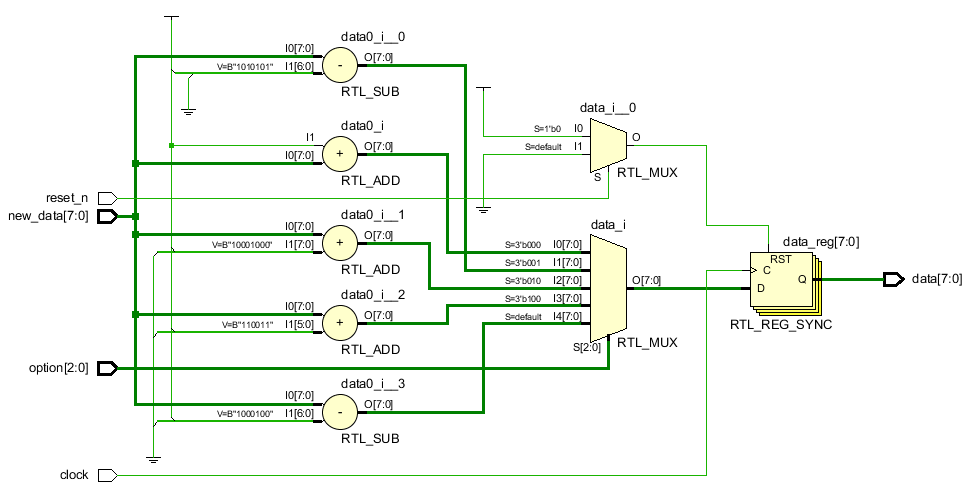

2. Ví dụ về 1 module đầy đủ có FlipFlop:

a, verilog code:

module flipflop(clock,

reset_n,

new_data,

option,

data

);

input clock;

input reset_n;

input [7:0] new_data;

input [2:0] option;

output [7:0] data;

wire clock;

wire reset_n;

wire [7:0] new_data;

wire [2:0] option;

reg [7:0] data;

always @ ( posedge clock ) begin

if ( ! reset_n ) begin

data <= 8'h00;

end

else begin

case ( option )

3'b000: data <= new_data + 8'h01;

3'b001: data <= new_data - 8'h55;

3'b010: data <= new_data + 8'h88;

3'b100: data <= new_data + 8'h33;

default: data <= new_data - 8'h44;

endcase

end

end

endmodule

b, schematic: ( Lấy từ Vivado )

Nguồn: degic.freeforums

Bạn Có Đam Mê Với Vi Mạch hay Nhúng - Bạn Muốn Trau Dồi Thêm Kĩ Năng

Mong Muốn Có Thêm Cơ Hội Trong Công Việc

Và Trở Thành Một Người Có Giá Trị Hơn

Bạn Chưa Biết Phương Thức Nào Nhanh Chóng Để Đạt Được Chúng

Hãy Để Chúng Tôi Hỗ Trợ Cho Bạn. SEMICON

Hotline: 0972.800.931 - 0938.838.404 (Mr Long)