Nếu các bạn có thể viết một vài dòng code, một vài logic and or not xor và flipflop, counter v.v, các bạn có thể suy nghĩ về cách mà người ta sẽ kiểm chứng về sự đúng đắn của logic đó. Trong thiết kế logic, bước này gọi là simulation hoặc verification. Trong đó, người ta thường dùng testbench.

1. Testbench là gì ?

Hiểu một cách đơn giản, testbench là một phương tiện dùng để kiểm tra logic của một thiết kế cụ thể.

Hiểu theo ngôn ngữ RTL, testbench là một module, dùng để cấp các tín hiệu đầu vào cho module được test, và thu thập các giá trị đầu ra của module đó, đồng thời, kiểm chứng được tính đúng đắn của logic từ các giá trị đầu ra đó.

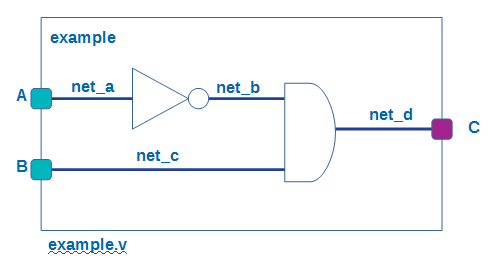

Các bạn có thể hình dung về testbench qua block diagram sau. Ví dụ có 1 module example như hình dưới:

module example (

A,

B,

C );

input A;

input B;

output C;

wire A;

wire B;

wire C;

assign C = B & ( ! A );

endmodule

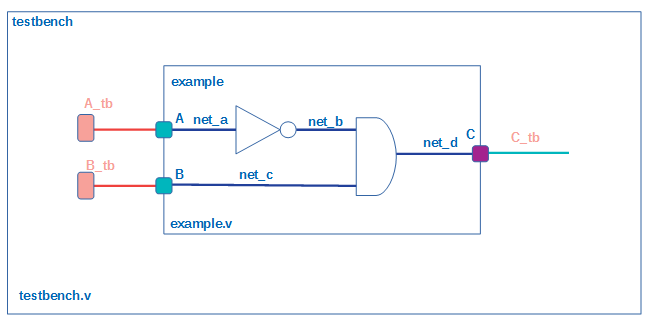

Testbench sẽ là phần lớn hơn, bao lấy example và có block diagram như sau:

Phần testbench sẽ có phần điều khiển là những tín hiệu nối với input của example, ở hình trên là A_tb và B_tb. Phần này cung cấp các trường hợp đầu vào theo yêu cầu. Giá trị đầu ra sẽ được lấy thông qua phần monitor, gồm những tín hiệu nối với đầu ra của example, C_tb.

2. Các thành phần trong testbench:

Về cấu trúc code, testbench bao gồm những phần cơ bản như sau:

module testbench ();

// A, phần khai báo tín hiệu điều khiển và monitor.

reg A_tb;

reg B_tb;

wire C_tb;

// B, phần gọi module

example example_01 (

.A ( A_tb),

.B ( B_tb),

.C ( C_tb)

);

// C, phần khởi tạo các giá trị ban đầu

initial begin

A_tb = 1'b0;

B_tb = 1'b0;

end

// D, phần thực thi chính của simulation

initial begin

#10; // đợi 10 đơn vị thời gian

A_tb = 1'b1;

B_tb = 1'b0;

#10; // đợi 10 đơn vị thời gian

A_tb = 1'b0;

B_tb = 1'b1;

#10; // đợi 10 đơn vị thời gian

A_tb = 1'b1;

B_tb = 1'b1;

#10; // đợi 10 đơn vị thời gian

A_tb = 1'b0;

B_tb = 1'b0;

$finish(); // kết thúc simulation

end

endmodule

A, Khai báo các tín hiệu của phần điều khiển và phần monitor.

- Tất cả các tín hiệu điều khiển ở testbench sẽ được khai báo ở dạng reg, để có thể được gán giá trị để truyền vào bên trong module test.

- Tín hiệu monitor thường được khai báo dạng wire, đây là phần tử thụ động, chỉ nhận giá trị từ output của module được test. Các phần khác sẽ dùng giá trị từ tín hiệu này để đánh giá, so sánh và đưa ra kết luận về tính đúng đắn của chức năng.

B, Phần gọi module được test. Phần này hay còn gọi là "instance"

- Cấu trúc của instance được viết như trên.

- Tên các tín hiệu ở testbench có thể giống với bên trong example module.

C, Phần khởi tạo tín hiệu điều khiểu.

- Tại thời điểm T = 0, các simulator hoặc phần mềm mô phỏng sẽ không hiểu được giá trị của các tín hiệu điều khiển này là bao nhiêu. Thông thường nó sẽ gán cho các tín hiệu này giá trị "X". Đây là giá trị thể hiện sự không xác định của tín hiệu. Nếu như không khởi tạo, các giá trị X này sẽ lan truyền vào bên trong module được test, sẽ gây ra các hoạt động không mong muốn.

- Để loại bỏ sự không xác định trên, chúng ta tốt nhất nên khởi tạo các đầu vào này theo một giá trị cụ thể là 0, hoặc 1.

D, Phần thực thi chính của simulation.

- Đây là nơi chứa các sự vận hành của việc kiểm tra.

- Thông thường, người chạy simulation phải có một kế hoạch hoặc là một ý tưởng test nào đó rõ ràng. Sau đó, các tín hiệu điều khiển liên quan sẽ được viết theo trình tự thời gian tương ứng với ý tưởng đó.

3. Kết quả của simulation

Kết quả của simulation có thể tồn tại ở 3 loại thông tin sau:

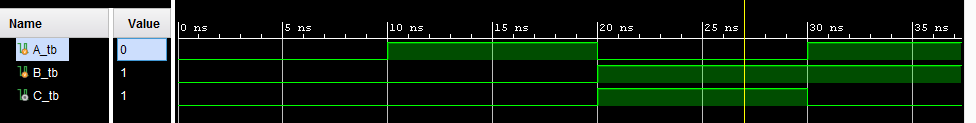

a, Waveform:

- Đây là dạng thông tin cơ bản nhất mà bạn nhận được khi chạy simulation. Bạn phải hiểu rõ các giá trị của tín hiệu theo từng thời điểm. Việc phân tích waveform đa phần là bằng mắt thường. Do đó, đòi hỏi phải có kỹ năng nhìn nhận waveform một các tinh tế.

b, Các thông báo của Tool trong quá trình chạy simulation:

- Các tool dùng để simulation thường sẽ có phần compile dành cho testbench. Do đó, nó có thể thông báo cho người dùng các vấn đề của code, syntax v.v. Người chạy simulation phải đọc hiểu và đánh giá cũng như có các động tác khắc phục lỗi, cảnh báo của tool.

c, Các loại output khác từ người dùng:

- Các loại này là tùy biến từ mong muốn của người dùng.

- Nó có thể bao gồm các thông báo dạng text, hoặc một file lưu các giá trị đầu ra, hoặc tín hiệu nào đó cụ thể.

Đây là waveform từ bước simulation của testbench phía trên:

Từ module thiết kế, các bạn có thể xác nhận lại logic của module có chính xác như những gì mình mong muốn hay chưa.

Đây chỉ là ví dụ để các bạn hiểu như thế nào là testbench và instance 1 design vào testbench.

Các bạn có thể dùng testbench này cho những simulator khác nhau và đều cho kết quả như nhau.

Nguồn: degic.freeforums

Bạn Có Đam Mê Với Vi Mạch hay Nhúng - Bạn Muốn Trau Dồi Thêm Kĩ Năng

Mong Muốn Có Thêm Cơ Hội Trong Công Việc

Và Trở Thành Một Người Có Giá Trị Hơn

Bạn Chưa Biết Phương Thức Nào Nhanh Chóng Để Đạt Được Chúng

Hãy Để Chúng Tôi Hỗ Trợ Cho Bạn. SEMICON

Hotline: 0972.800.931 - 0938.838.404 (Mr Long)