Cách tạo module và instance của 1 module trên Verilog

1. Định nghĩa:

- Module là một đơn vị design nhỏ nhất có trong thiết kế phần cứng.

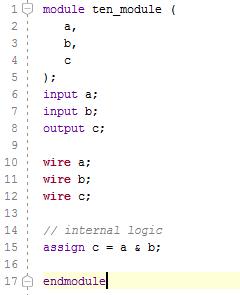

2. Syntax của module:

- Các thành phần của một module:

+ Tên module. Được khai báo sau từ khóa "module" của verilog

+ Danh sách các port được liệt kê trong cặp dấu "(" ")"

+ Danh sách các port đi kèm với chiều của port ( input, output hoặc inout )

+ Khai báo loại tín hiệu ( thông thường là wire hoặc reg )

+ Các cấu trúc logic bên trong của module

- Để khai báo module, các bạn xem ví dụ sau đây. Chúng ta sẽ khai báo 1 module tên là "ten_module".

Chức năng của module này tương tự như cổng logic AND: c = a & b;

Trong đó, a và b là đầu vào ( input ), c là đầu ra ( output )

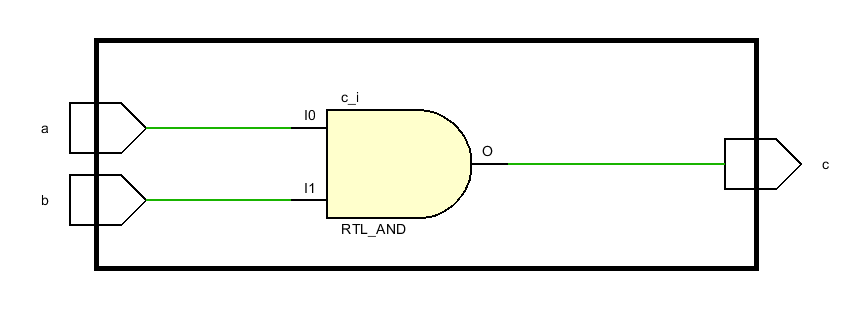

3. Sơ đồ khối của module (Block Diagram)

4. Instance của một module vào module cấp trên:

Trong thực tế, một module thường là một nhóm logic có chức năng cụ thể và thường có khối lượng logic vừa phải để có thể kiểm soát được. Khi khối lượng design quá lớn, người ta sẽ nghĩ đến việc chia nhỏ module ra thành nhiều module con, để dễ dàng quản lý được chức năng của chúng, cũng như tiện cho việc quan sát, simulation và review lại code. Khi đó, các module con sẽ được gọi vào module mẹ thông qua instance.

Ngoài ra, khi mà cùng một mạch logic mà được sử dụng lại nhiều lần ở các module khác nhau, thì designer chỉ cần code cho 1 module. Sau đó, nơi nào cần sử dụng sẽ gọi module đó thông qua instance.

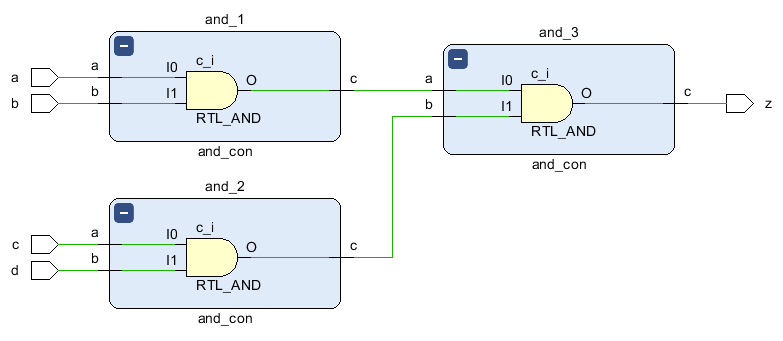

Ví dụ:

Design này gồm 3 cổng AND giống nhau về chức năng, do đó chúng ta chỉ cần code cho 1 module and_con và module "ten_module". Trong module "ten_module", chúng ta sẽ gọi module and_con vào, thành 3 instances tên là and_1, and_2 và and_3. Khi đó, nhìn từ module mẹ, chúng ta sẽ thấy được 3 instances bên trong. Khi đi vào từng instance, chúng ta sẽ thấy được cổng AND như nhau. Đó là vì cả 3 instance này đều trỏ về module and_con.

Chúng ta có một thiết kế có block diargram bên dưới. Đầu vào a,b,c,d và đầu ra là z. Logic thì rõ ràng như hình:

Verilog code của instance:

Giả dụ ta đã có module and_con như là module được viết ở mục 2. Khi muốn đặt một instance của module and_con vào module "ten_module", chúng ta truyền từng tín hiệu ở ngoài module ten_module vào module and_con. Để khai báo tên của instance, chúng ta đặt tên instance ngay sau tên module and_con. Bây giờ, module ten_module sẽ có dạng như thế này:

module ten_module (

a,

b,

c,

d,

z

);

input a;

input b;

input c;

input d;

output z;

wire a;

wire b;

wire c;

wire d;

wire z;

wire f;

wire g;

// internal logic

and_con and_1 (

.a ( a ),

.b ( b ),

.c ( f )

);

and_con and_2 (

.a ( c ),

.b ( d ),

.c ( g )

);

and_con and_3 (

.a ( f ),

.b ( g ),

.c ( z )

);

endmodule // end ten_module

// start of and_con module

module and_con (

a,

b,

c

);

input a;

input b;

output c;

wire a;

wire b;

wire c;

// internal logic

assign c = a & b;

endmodule

Thông tin thêm:

- Ngoài 2 loại cổng input, output, trong verilog còn có 1 loại nữa là inout để thể hiện cho loại tín hiệu có cả hai chiều vào ra.

Nguồn: degic.freeforums

Mong Muốn Có Thêm Cơ Hội Trong Công Việc

Và Trở Thành Một Người Có Giá Trị Hơn

Bạn Chưa Biết Phương Thức Nào Nhanh Chóng Để Đạt Được Chúng

Hãy Để Chúng Tôi Hỗ Trợ Cho Bạn. SEMICON

Hotline: 0972.800.931 - 0938.838.404 (Mr Long)