Hàm random được sử dụng để tạo ra các giá trị ngẫu nhiên. Mục đích của hàm random có thể được sử dụng để cho quá trình kiểm tra thiết kế một cách ngẫu nhiên, bằng cách đưa vào các input ngẫu nhiên. Ví dụ sử dụng hàm random để tạo address và data ngẫu nhiên như sau sau:

module top();

reg clk;

reg [31:0] data;

reg [31:0] address;

initial begin

clk = 0;

$monitor(“display time = %d; data = %h ; address = %h;”, $time,data,address);

end

always #5 clk = ~clk;

initial

begin

repeat(10)@(posedge clk) begin

data = $random;

address = $random;

end

$finish;

end

endmodule

Một kết quả output của ví dụ trên

display time = 0; data = xxxxxxxx ; address = xxxxxxxx;

display time = 5; data = 12153524 ; address = c0895e81;

display time = 15; data = 8484d609 ; address = b1f05663;

display time = 25; data = 06b97b0d ; address = 46df998d;

display time = 35; data = b2c28465 ; address = 89375212;

display time = 45; data = 00f3e301 ; address = 06d7cd0d;

display time = 55; data = 3b23f176 ; address = 1e8dcd3d;

display time = 65; data = 76d457ed ; address = 462df78c;

Bằng cách sử dụng hàm random và các điều kiện kèm theo, chúng ta có thể tạo ra được các giá trị ngẫu nhiên trong một khoảng xác định nào đó. Ví dụ như việc giới hạn lại vùng địa chỉ (address) truy cập thanh ghi.

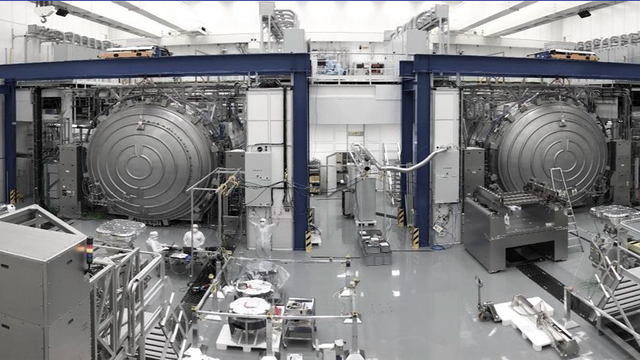

Bạn có đam mê ngành thiết kế vi mạch và bạn muốn có mức lương1000 usd

hãy đến với ngành vi mạch tại SEMICON