Introduction

Let's assume that we have a design which requires us to have counters of various width, but with the same functionality.

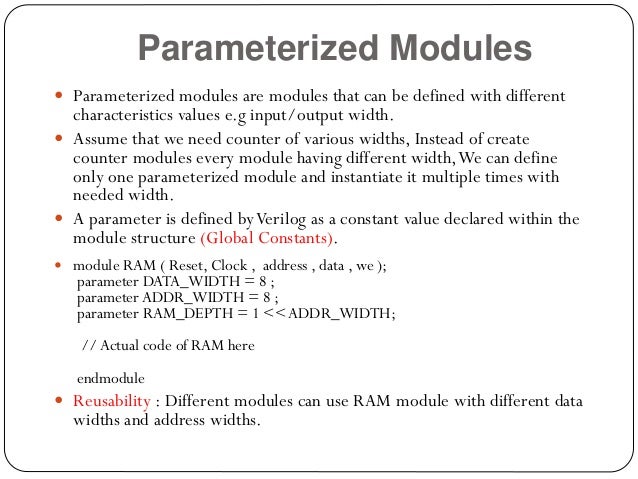

Maybe we can assume that we have a design which requires lots of instants of different depth and width of RAMs of similar functionality. Normally what we do is creating counters of different widths and then use them. The same rule applies to the RAM we talked about.

| But Verilog provides a powerful way to overcome this problem: it provides us with something called parameter; these parameters are like constants local to that particular module. |

| We can override the default values, either using defparam or by passing a new set of parameters during instantiation. We call this parameter overriding. |

Parameters

A parameter is defined by Verilog as a constant value declared within the module structure. The value can be used to define a set of attributes for the module which can characterize its behavior as well as its physical representation.

- Defined inside a module.

- Local scope.

- Maybe overridden at instantiation time.

- If multiple parameters are defined, they must be overridden in the order they were defined. If an overriding value is not specified, the default parameter declaration values are used.

| |||||

1 module secret_number; 2 parameter my_secret = 0; 3 4 initial begin 5 $display("My secret number is %d", my_secret); 6 end 7 8 endmodule 9 10 module defparam_example(); 11 12 defparam U0.my_secret = 11; 13 defparam U1.my_secret = 22; 14 15 secret_number U0(); 16 secret_number U1(); 17 18 endmodule

1 module secret_number; 2 parameter my_secret = 0; 3 4 initial begin 5 $display("My secret number in module is %d", my_secret); 6 end 7 8 endmodule 9 10 module param_overide_instance_example(); 11 12 secret_number #(11) U0(); 13 secret_number #(22) U1(); 14 15 endmodule

1 module ram_sp_sr_sw ( 2 clk , // Clock Input 3 address , // Address Input 4 data , // Data bi-directional 5 cs , // Chip Select 6 we , // Write Enable/Read Enable 7 oe // Output Enable 8 ); 9 10 parameter DATA_WIDTH = 8 ; 11 parameter ADDR_WIDTH = 8 ; 12 parameter RAM_DEPTH = 1 << ADDR_WIDTH; 13 // Actual code of RAM here 14 15 endmodule

1 module ram_controller ();//Some ports 2 3 // Controller Code 4 5 ram_sp_sr_sw #(16,8,256) ram(clk,address,data,cs,we,oe); 6 7 endmodule

In Verilog 2001, the code above will work, but the new feature makes the code more readable and error free. 1 module ram_controller ();//Some ports 2 3 ram_sp_sr_sw #( 4 .DATA_WIDTH(16), 5 .ADDR_WIDTH(8), 6 .RAM_DEPTH(256)) ram(clk,address,data,cs,we,oe); 7 8 endmodule |

Bạn Có Đam Mê Với Vi Mạch hay Nhúng - Bạn Muốn Trau Dồi Thêm Kĩ Năng

Mong Muốn Có Thêm Cơ Hội Trong Công Việc

Và Trở Thành Một Người Có Giá Trị Hơn