Introduction

A compiler directive may be used to control the compilation of a Verilog description. The grave accent mark, `, denotes a compiler directive.

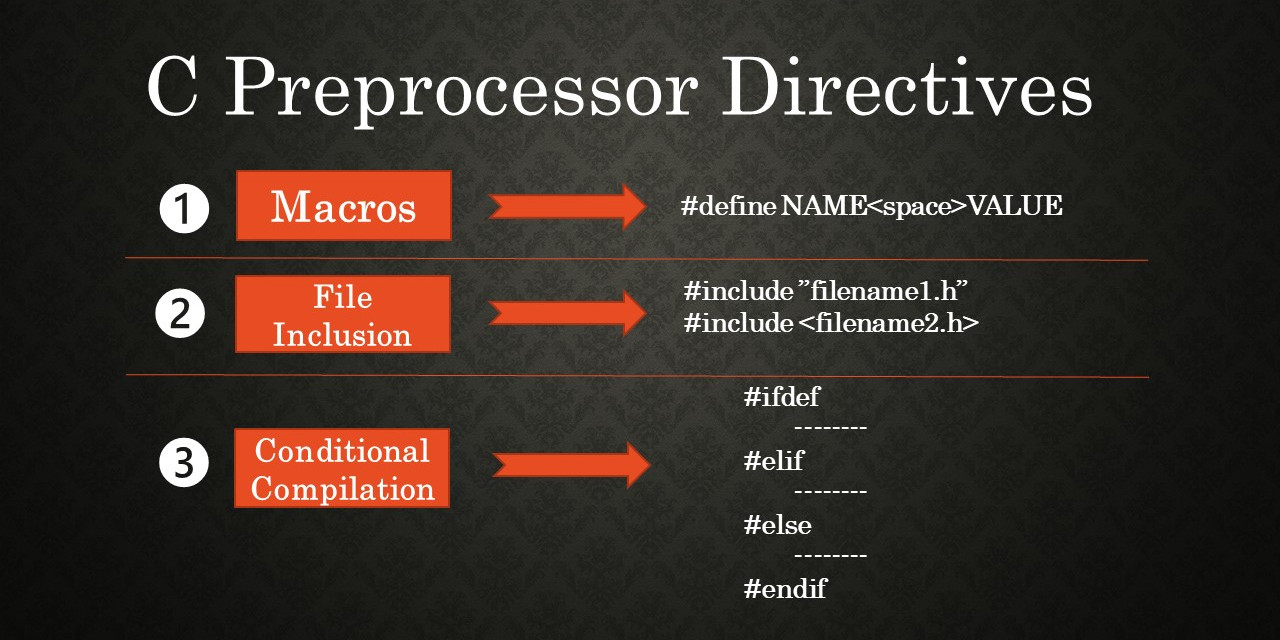

A directive is effective from the point at which it is declared to the point at which another directive overrides it, even across file boundaries. Compiler directives may appear anywhere in the source description, but it is recommended that they appear outside a module declaration. This appendix presents those directives that are part of IEEE-1364.

| As in any language, each compiler has its own way of handling command line options and supported compiler directives in code. Below we will see some standard and common compiler directives. For specific compiler directives, please refer to simulator manuals. | |||||||||||||||||||||||||

| `include The `include compiler directive lets you insert the entire contents of a source file into another file during Verilog compilation. The compilation proceeds as though the contents of the included source file appear in place of the `include command. You can use the `include compiler directive to include global or commonly-used definitions and tasks, without encapsulating repeated code within module boundaries.

| |||||||||||||||||||||||||

Bạn Có Đam Mê Với Vi Mạch hay Nhúng - Bạn Muốn Trau Dồi Thêm Kĩ Năng

Mong Muốn Có Thêm Cơ Hội Trong Công Việc

Và Trở Thành Một Người Có Giá Trị Hơn