The term Asic stands for Application Specific Integrated Circuit. Is an integrated circuit (IC) customized for a particular use, rather than intended for general-purpose use. Generally an ASIC design will be undertaken for a product that will have a large production run,

and the ASIC may contain a very large part of the electronics needed on a single integrated circuit. As feature sizes have shrunk and design tools improved over the years, the complexity in an ASIC has grown from 5,000 over 100 million gates

Â

Mrd

A Marketing Requirements Document (MRD) outlines the requirements a new product. Engineers use an MRD to create the product. Marketing requirement document covers market needs, the customer value proposition, and product functionality. It is developed by the Marketing team and upper management.

Â

Architecture Specification

The architect based on the MRD specification, develops the overall architecture of the chip. This is a very high level plan. Architecture Specification includes functional descriptions of each module, Properties and weights.

Design Specification

The designers and architects sit together to come up with detailed design documents. Design strategies, design partitions, type of memories to use, etc.

Verification Plan

A Verification specification is called a Verification/test plan. The verification engineer goes through all the above documents and prepares verification plan to verify the design.

Rtl Design

Â

RTL stands for Register Transfer Level. The designer starts implementing the RTL design in HDL like verilog or VHDL.

Â

Functional Verification

The verification engineers starts developing TestBench and verifies whether the DUT works according to specification or not.

Â

Synthesis

Synthesis is the process of taking a design written in a hardware description language, compiling it into a net list of interconnected gates which are selected from a user-provided library of various gates. The design after synthesis is a gate-level design.

Â

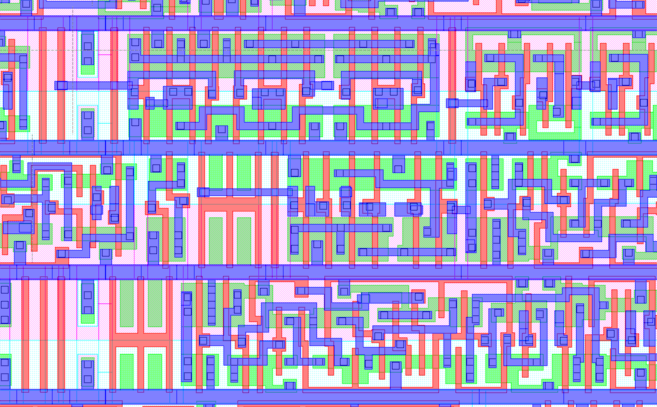

Physical Design

Physical design process includes logic partitioning, floor planning, global routing, detailed routing, compaction, and performance-driven layout. PD team transforms net list representation of a system into layout representation.

Â

Timing Analysis

Â

Static timing analysis is an important step in analyzing the performance of a design. In the Timing analysis Setup time, hold time ,recovery time ,removal time , Clock latency, clock skew, clock uncertainty etc checks are done.

Â

Tapeout

This is the final stage of the design cycle of integrated circuits. Once all the checks are done, the design is ready to be sent to Foundry.

Â