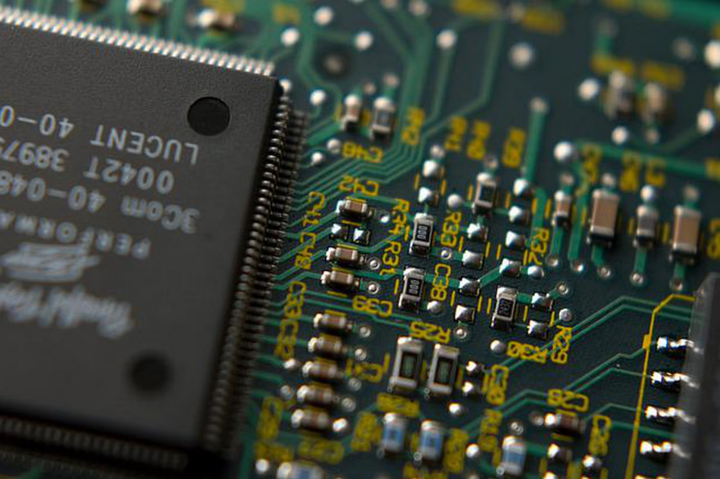

Dù cho định nghĩa về tên nốt có như thế nào đi chăng nữa thì các con số trong đó vẫn tiếp tục giảm xuống. Cùng với chúng, khoảng cách giữa các transistor và giữa các dây dẫn gần nhất trên con chíp cũng được thu hẹp lại. Chúng quy định mật độ của một con chíp và do đó, số lượng transistor có thể đặt thêm lên một tấm (wafer) silicon hòng giảm giá thành.

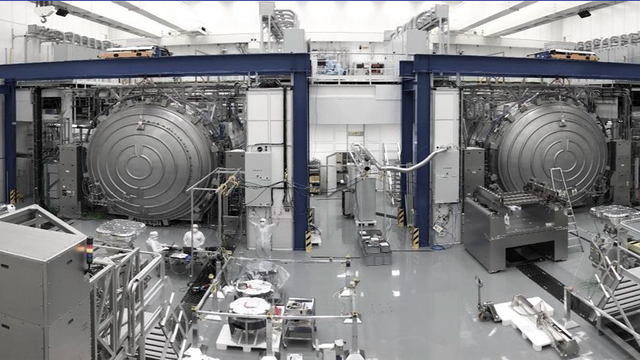

Tuy nhiên trở ngại cố hữu lại nằm ở việc tạo hình các chi tiết mạch ngày càng nhỏ này. “Khi xuống tới mức khoảng 28nm, chúng tôi đã thực sự đạt tới giới hạn của các máy khắc cực tím (lithographic tools),” theo Subramani Kengeri, Phó Giám đốc về kiến trúc công nghệ cao cấp của GlobalFoundries, công ty chíp lớn thứ hai trên thế giới, chỉ sau TSMC.

Để đối phó với trở ngại này, Kengeri cùng đồng nghiệp buộc phải sử dụng tới một kỹ thuật về khắc cực tím gọi là tạo hình kép (double patterning). Kỹ thuật này cho phép khắc các chi tiết nhỏ bằng cách chia một bước tạo hình ra thành hai. Việc tạo hình chi tiết mạch dựa trên phần sai lệch nhỏ giữa hai bước này.

Intel đã sử dụng kỹ thuật này để tạo nên các transistor trong các con chíp 22nm của họ, nhưng họ vẫn sử dụng kỹ thuật tạo hình đơn để hình thành lớp kim loại dày đặc nhất. Sử dụng kỹ thuật này ở mức tới hạn, công ty này tạo nên các dây dẫn có kích thước một “quãng” là 80nm. Kích thước này bao gồm chiều rộng của một dây dẫn và khoảng cách tới dây bên cạnh. Sử dụng tạo hình kép, GlobalFoundries và các công ty khác giảm được kích thước quãng ở các con chíp 20nm xuống còn 64nm. Nhưng một nhược điểm lớn của việc này là chế tạo chíp dùng tạo hình kép tốn nhiều thời gian hơn, do đó làm tăng đáng kể giá thành.

Tiếp tục sử dụng kỹ thuật này ở nốt 14nm đồng nghĩa với việc họ này phải áp dụng nó cho nhiều lớp vật liệu của chíp hơn nữa. Bởi vậy mà năm ngoài (2012), Kengeri và các đồng nghiệp tiên phong công bố rằng: Họ sẽ không tiếp tục thu nhỏ các kích thước nữa.

Hai loại transistor: Các công ty sản xuất chíp đang trong quá trình chuyển đổi từ transistor dạng planar (kênh phẳng) truyền thống [trái] sang dạng có kênh lồi [phải]. Intel công bố về loại transistor 3-D này năm 2011, và hiện nay chúng đang được bán ra khá rộng rãi. Các công ty lớn khác như GlobalFoundries, Samsung, và Taiwan Semicondutor Manufacturing Co. (TSMC), thì đang đẩy mạnh sản lượng của các chíp 20nm dùng transistor kênh phẳng. Họ sẽ chuyển qua dùng transistor 3-D ở thế hệ kế tiếp.

Minh họa: Emily Cooper

Dòng chíp 14nm của GlobalFoundries, được dự tính bắt đầu đi vào sản xuất năm 2014, nhiều khả năng sẽ là lần đầu tiên, dùng các transistor FinFET. Tuy nhiên, công ty này sẽ sử dụng dây dẫn có mật độ của nốt 20nm để chế tạo các con chíp mới này. “Thực chất thế hệ FinFET đầu tiên sẽ tái sử dụng lại hết (nền tảng của nốt 20nm) và chỉ đưa vào FinFET vào khung công nghệ có sẵn này,” Kengeri nói. “Nói theo cách khác thì nó thực ra là FinFET 20nm.” Dẫu vậy công ty này vẫn gọi chúng là chíp 14nm vì hiệu suất và mức tiết kiệm điện của chúng là tương đương với chíp ở một thế hệ thấp hơn của dòng 20nm thông thường.

Hai loại transistor: Các công ty sản xuất chíp đang trong quá trình chuyển đổi từ transistor dạng planar (kênh phẳng) truyền thống [trái] sang dạng có kênh lồi [phải]. Intel công bố về loại transistor 3-D này năm 2011, và hiện nay chúng đang được bán ra khá rộng rãi. Các công ty lớn khác như GlobalFoundries, Samsung, và Taiwan Semicondutor Manufacturing Co. (TSMC), thì đang đẩy mạnh sản lượng của các chíp 20nm dùng transistor kênh phẳng. Họ sẽ chuyển qua dùng transistor 3-D ở thế hệ kế tiếp.

Kengeri hi vọng rằng bằng việc trì hoãn thu nhỏ các con chíp và tập trung vào phát triển transistor 3-D, GlobalFoundries sẽ bắt kịp Intel, công ty đã đang bán đại trà chíp 22nm sử dụng linh kiện 3-D. Chíp 14nm của GlobalFoundries không hề dày đặc hơn. Do đó có giá thành tương đương với các chíp thuộc thế hệ trước. Tuy nhiên chúng vẫn là một bước tiến lớn, Kengeri nói. “Quan điểm của chúng tôi—với sự đồng tình của khách hàng—là miễn sao họ thấy được lợi ích, họ không quan tâm tới tên của công nghệ hay những chi tiết nội tại.”

“Đây là một động thái khá gây tranh cãi,” William Arnold, chuyên gia trưởng của ASML, công ty sản xuất thiết bị chế tạo bán dẫn lớn nhất thế giới. “các khách hàng của các công ty sản xuất chíp, các công ty sản xuất link kiện điện thoại di động, tỏ ra hoài nghi về việc không thu nhỏ kích thước mà vẫn cải thiện được hiệu suất chíp. Họ nói khá rõ là họ không vui về điều này.”

Không kể tới động thái mới đây của các công ty chíp, thì chíp ngày nay vẫn ít nhiều nhân đôi mật độ từ nốt này qua nốt khác, Andrew Kahng, Giáo sư của Đại học California, San Diego, một chuyên gia thiết kế chíp có hiệu suất cao, nhận định. Nhưng theo Kahng thì có một vấn đề sâu sa hơn ẩn sau những cái tên giảm dần đều này. Ông nói, có sự khác biệt giữa mật độ lý thuyết(available density)-mật độ mạch và dây dẫn có thể tạo nên được trên chíp- và mật độ khả dụng(realizable density)-mật độ mạch thực tế có thể sử dụng cho một sản phẩm có tính cạnh tranh trên thị trường.

Do các chíp mới nhất hiện nay có mật độ mạch và năng lượng cực cao, nên các kỹ sư thiết kế buộc phải dùng thêm các mạch sửa lỗi, mạch dự phòng, các mạch hỗ trợ đọc/ghi cho các tế bào RAM bị yếu, các mạch theo dõi và tự điều chỉnh khi hiệu năng thay đổi, cùng với các cấp bậc bộ nhớ phức tạp để đáp ứng được các kiến trúc chíp đa nhân. Theo Kahng, vấn đề ở đây là “những mạch phụ trợ này làm tăng diện tích chíp.” Nhóm nghiên cứu của ông đã tìm hiểu các chi tiết kỹ thuật và phân tích những hình chụp của các con chíp nhiều năm nay, và họ đi tới một kết luận không mấy vui: Nếu bạn tính thêm cả các mạch phụ trợ nói trên thì mật độ của chíp không tăng gấp hai lần qua các thế hệ. Trên thực tế, phân tích của Kahng cho thấy mức tăng mật độ của các chíp thuộc ba thế hệ từ nay về trước (2007), chỉ vào khoảng 1.6 chứ không phải là 2. Mật độ chíp thấp này đồng nghĩa với giá thành chíp cao hơn, đồng thời làm giảm hiệu suất của chíp do phải truyền tín hiệu đi xa hơn. Theo Kahng, lượng thâm hụt về hiệu suất này đồng nhất tới mức có thể coi như là một quy luật khác(như Luật Moore).

Tuy vậy, vẫn có thể thu hồi tổn thất này lại được. Kahng nói, cho tới nay ngành công nghiệp chíp ưu tiên để theo kịp Luật Moore, các công ty cho ra mắt các dòng sản phẩm sử dụng các quy trình chế tạo mới sau mỗi 1 năm rưỡi hay 2 năm. Như vậy là không có đủ thời gian để tìm tòi các kỹ thuật thiết kế giúp giảm năng lượng tiêu hao hay tăng cường hiệu suất chíp. “Bạn không có thời gian để tối ưu hóa mọi thứ với lịch làm việc như vậy,” ông nhận xét. Theo Kahng, do giá trị của việc đơn thuần thu nhỏ giảm dần, các công ty nên xem xét lại các thiết kế và phát triển các phương thức cải thiện hiệu suất mới hoặc các phương thức họ chưa kịp thực hiện trước đó.

Vậy khi nào thì việc thu nhỏ kích thước chíp thực sự ngừng? Hiện nay, công nghệ tạo hình bán dẫn, sử dụng các tia laser có bước sóng 193nm, đang ngày càng trở nên đắt đỏ. Trong khi thế hệ công nghệ kế tiếp mặc định của nó là công nghệ khắc siêu cực tím (extreme ultraviolet lithography) có bước sóng ngắn hơn thì đã bị trì hoãn từ rất lâu.

Kahng cho rằng, vài năm tới, trong khi nỗ lực thu nhỏ của các công ty chíp vượt qua mức 10nm, họ có thể vấp phải trở ngại ở việc đi dây trước tiên. Mỗi dây dẫn bằng đồng cần có một lớp vỏ bảo vệ giúp cho kim loại này không rò rỉ ra xung quanh, đồng thời giúp cách điện với các dây dẫn kề bên. Lớp bảo vệ này phải tương đối dày thì mới hiệu quả. Do đó, độ dày tối thiểu này sẽ là giới hạn cực tiểu của khoảng cách giữa các dây và buộc phần đồng để truyền tín hiệu phải thu nhỏ lại. Điều này khiến điện trở của dây dẫn và độ trễ của tín hiệu tăng đáng kể, ảnh hưởng lớn tới hiệu suất chíp. Kahng cho biết, dù cho giới nghiên cứu đang thử nghiệm các vật liệu thay thế khác, thì vẫn chưa rõ liệu chúng có kịp sẵn sàng để theo kịp tốc độ không đổi của Luật Moore hay không.

Rất nhiều người trong ngành bán dẫn đã chứng kiến hết trở ngại này đến trở ngại khác xuất hiện để rồi luôn vượt qua được nhờ các cải tiến trong công nghệ nên họ phản đối việc đặt một thời điểm cụ thể khi Luật Moore hết hiệu lực. “Cứ mỗi thế hệ lại có người phán rằng chúng ta không thể thu nhỏ thêm được nữa,” Arnol của ASML nói, “nhưng lần nào cũng có các cải tiến công nghệ xuất hiện kịp lúc. Tôi vẫn chưa thấy đoạn kết của con đường.”

Tuy vậy, đối với những người theo sát lộ trình này thì những cột mốc trên đó đang càng ngày càng mờ nhạt.

Nguồn: https://chuyenmuccongnghe.com

Bạn Có Đam Mê Với Vi Mạch hay Nhúng - Bạn Muốn Trau Dồi Thêm Kĩ Năng

Mong Muốn Có Thêm Cơ Hội Trong Công Việc

Và Trở Thành Một Người Có Giá Trị Hơn

Bạn Chưa Biết Phương Thức Nào Nhanh Chóng Để Đạt Được Chúng

Hãy Để Chúng Tôi Hỗ Trợ Cho Bạn. SEMICON

Hotline: 0972.800.931 - 0938.838.404 (Mr Long)